#### **Second Edition - August 1984**

This manual describes the KD32-AA and KD32-AB central processing units used in the MicroVAX I.

# MicroVAX I CPU Technical Description

Document Order Number: EK-KD32A-TD-002

digital equipment corporation maynard, massachusetts

## First Edition, January 1984 Second Edition, August 1984

## Copyright © 1984 by Digital Equipment Corporation All rights reserved.

The material in this manual is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this manual.

#### Printed in U.S.A.

### The following are trademarks of Digital Equipment Corporation:

| DATATRIEVE   | DECwriter    | P/OS         | VMS            |

|--------------|--------------|--------------|----------------|

| DEC          | DIBOL        | Professional | VT             |

| DECmate      | digital      | Rainbow      | Work Processor |

| DECnet       | LSI-11       | RSTS         |                |

| DECset       | MASSBUS      | RSX          |                |

| DECsystem-10 | MICRO/PDP-11 | ULTRIX       |                |

| DECSYSTEM-20 | MicroVAX I   | UNIBUS       |                |

| DECtape      | MicroVMS     | VAX          |                |

| DECUS        | PDP          | VAXELN       |                |

|              |              |              |                |

## **Contents**

#### **Preface**

## **Chapter 1: Introduction** System Overview, 1-1 Processor, 1-2 Q22 Bus, 1-5 RODX1 Controller, 1-5 RX50 Diskette Drive, 1-5 RD51 and RD52 Fixed Disk Drives, 1-6 Memory, 1-7 Console Terminal, 1-7 Front Control Panel, 1-7 Patch Panel Assembly, 1-8 Backplane, 1-11 Power Supply, 1-12 System Architecture, 1-13 MicroVAX Architecture, 1-13 MicroVAX I Implementation, 1-16 System Timing, 1-17 System Bus Summary, 1-21 **Chapter 2: Programming Interface** Physical Address Space, 2-1 Address Translation, 2-2 I/O Space Programming Constraints, 2-7 Internal Processor Registers, 2-7

Interval Clock Control/Status Register, 2-13

Machine Check Error Summary Register, 2-14

Cache Disable Register, 2-13

Initialize Bus Register, 2-14

System Identification Register, 2-15 Console Terminal Registers, 2-15 Console Receive Control/Status Register (RXCS), 2-16 Console Receive Data Buffer Register (RXDB), 2-16 Console Transmit Control/Status Register (TXCS), 2-17 Console Transmit Data Buffer Register (TXDB), 2-17

MicroVAX I System Bootstrap, 2-19

Bootstrapping Methods, 2-20

Boot Command, 2-22

**Bootstrap Operation, 2-25**

Booting from Disk, 2-26

Booting from an MRV11-D PROM Module, 2-31

Booting from DEQNA, 2-32

Interface Between Primary and Secondary Bootstrap, 2-35

Microverify, 2-39

Console Terminal Messages, 2-40

LEDs, 2-40

Modes of Operation, 2-42

Console Microcode, 2-47

Console Terminal Modes, 2-47

Console Halt Codes. 2-48

Bit-mapped Video Interface, 2-49

Interrupts and Exceptions, 2-52

Interrupts, 2-52

Exceptions, 2-54

Arithmetic Traps/Faults, 2-54

Memory Management Exceptions, 2-55

Operand Reference Exceptions, 2-56

Instruction Execution Exceptions, 2-57

Trace Faults, 2-58

Instruction Emulation Exceptions, 2-58

System Failure Exceptions, 2-61

System Control Block, 2-69

System Control Block Base Register, 2-69

System Control Block Vectors, 2-69

## **Chapter 3: Processor Configuration**

Processor Configuration Overview, 3-1

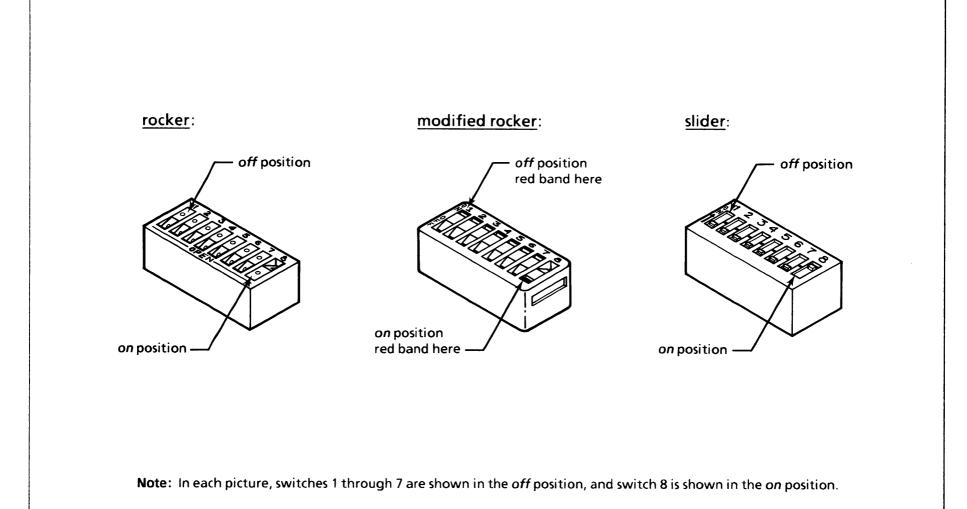

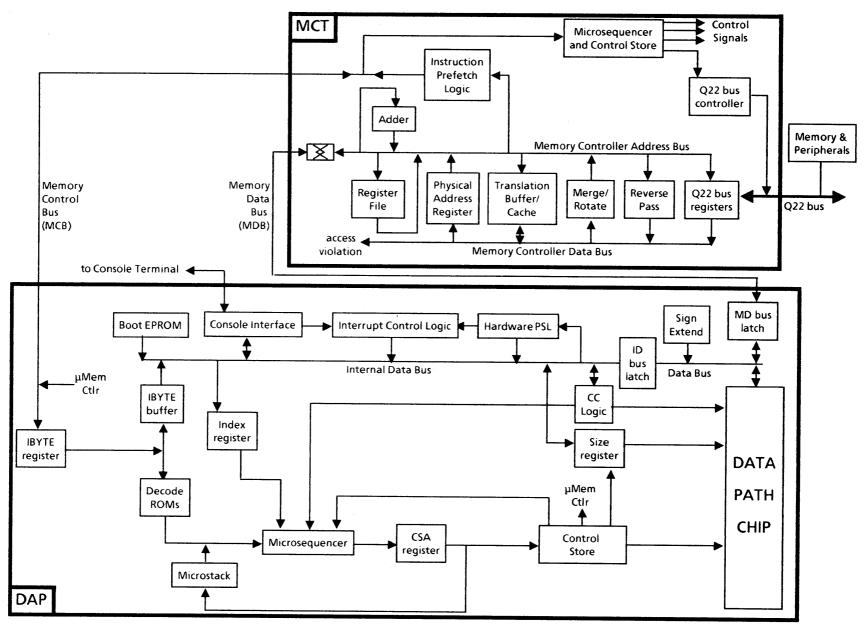

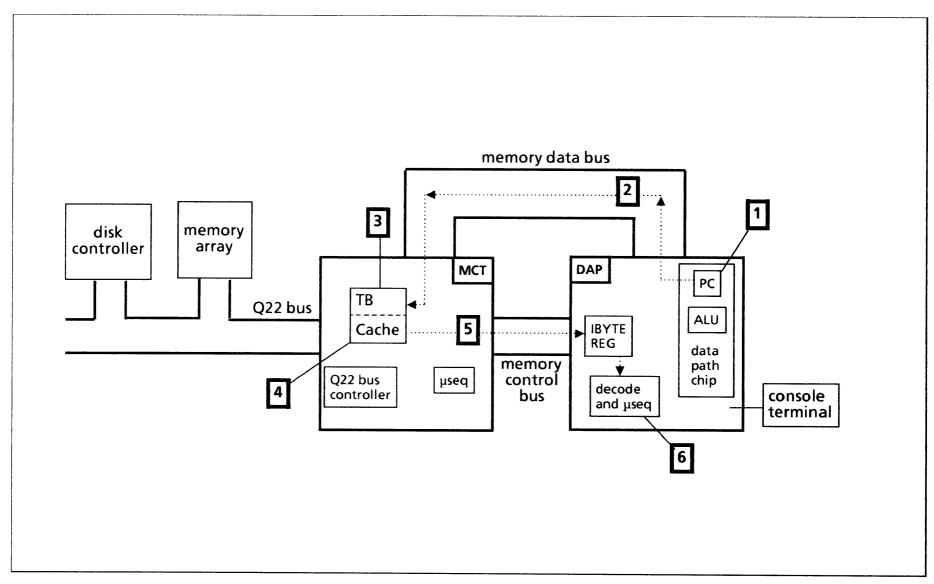

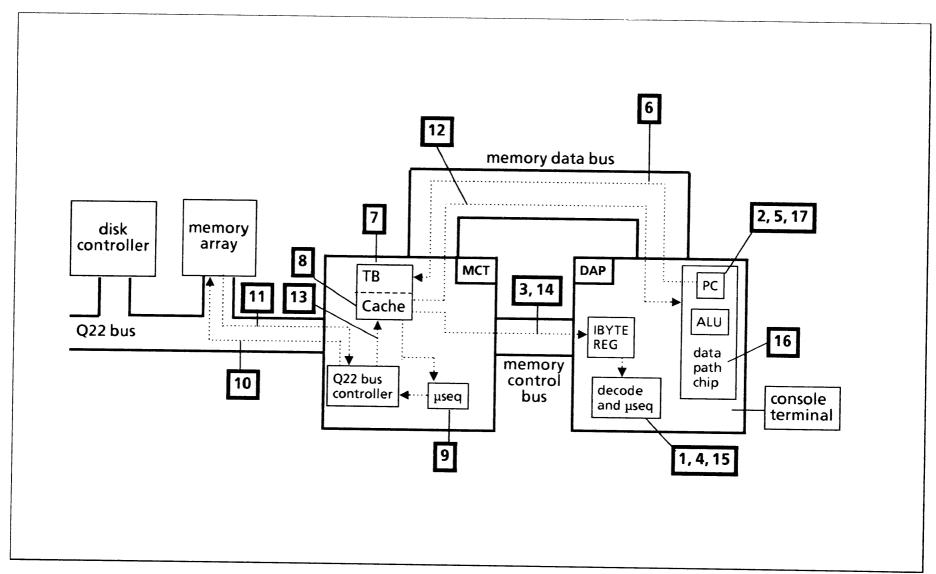

Option Switches, 3-2 Baud Rate Select, 3-5 Break Detect, 3-6 Recovery Action, 3-7 Warm Start, Boot, Halt, 3-7 Boot, Halt, 3-8 Warm Start, Halt, 3-8 Halt, 3-8 Console Terminal Type, 3-9 Bootstrap Search Order, 3-9 Resetting the Option Switches, 3-10 Rocker Switches, 3-13 Modified Rocker Switches, 3-13 Slider Switches, 3-14 Power and Cooling, 3-15 **Chapter 4: Functional Overview** Data Path, 4-1 Data Path Chip, 4-2 Control Store, 4-5 Microsequencer, 4-5 Instruction Decode Logic, 4-5 Internal Data Bus, 4-5 Boot EPROM, 4-6 Console Interface, 4-6 Memory Controller, 4-6 Cache, 4-8 Translation Buffer, 4-8 Memory Controller Micromachine, 4-8 Q22 Bus Interface Logic, 4-8 O22 Bus Interface, 4-9 Data Flow Overview, 4-9 Prefetch Operation, 4-10 Move Byte, 4-15 Subtract One and Branch, 4-21 Microcode, 4-27

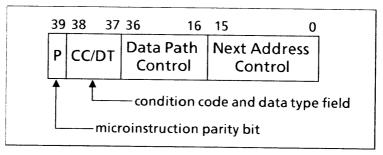

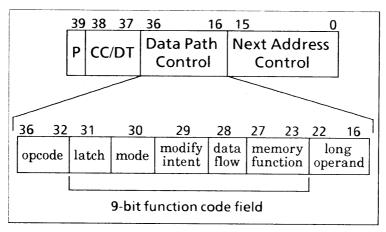

## **Chapter 5: Data Path Microcode**

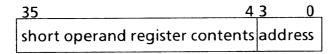

Microinstruction Format, 5-1 Parity Field, 5-2 Condition Code/Data Type Field, 5-2 Data Path Control Field, 5-4 Next Address Control Field, 5-9 Jump and Jump to Subroutine, 5-13 Branch, 5-13 Case, 5-14 Branch to Subroutine, 5-15 Trap, 5-15 Return, 5-15 Instruction Read and Decode (IRD), 5-16 Operand Specifier Decode, 5-17 Data Path Microinstructions, 5-18 ALU Microinstructions, 5-18 Shift Microinstructions, 5-18 Move Microinstructions, 5-19 Other Microinstructions, 5-19 Decode, 5-20 Restore, 5-22 Multiply Step, 5-23 Memory Request, 5-24 I-stream Request, 5-25 Operand Field Encoding, 5-26 Memory Controller Interface Microcode, 5-29 Memory Function Encoding, 5-30 Memory Functions, 5-33 READ. VECTOR, 5-33 VREAD.RCHECK, 5-33 VREAD.WCHECK, 5-34 VWRITE.WCHECK, 5-34 VREAD.LOCK, 5-35 IB.REFILL, 5-35 PREAD, 5-36 PWRITE, 5-36

XLATE.RCHECK, 5-37 XLATE.WCHECK, 5-37 IB.READ, 5-38 REPEAT.FIRST, 5-39 REPEAT.SECOND, 5-40 READ.CACHE, 5-41 WRITE.CACHE, 5-41 WRITEP, 5-41 Read MCT Registers, 5-42 Write MCT Registers, 5-42 READ.TB, 5-43 WRITE.TB, 5-43 INVALID.SINGLE, 5-44 INVALID.MULTIPLE, 5-44 RCHECK, 5-45 WCHECK, 5-45 Memory Controller Status, 5-46

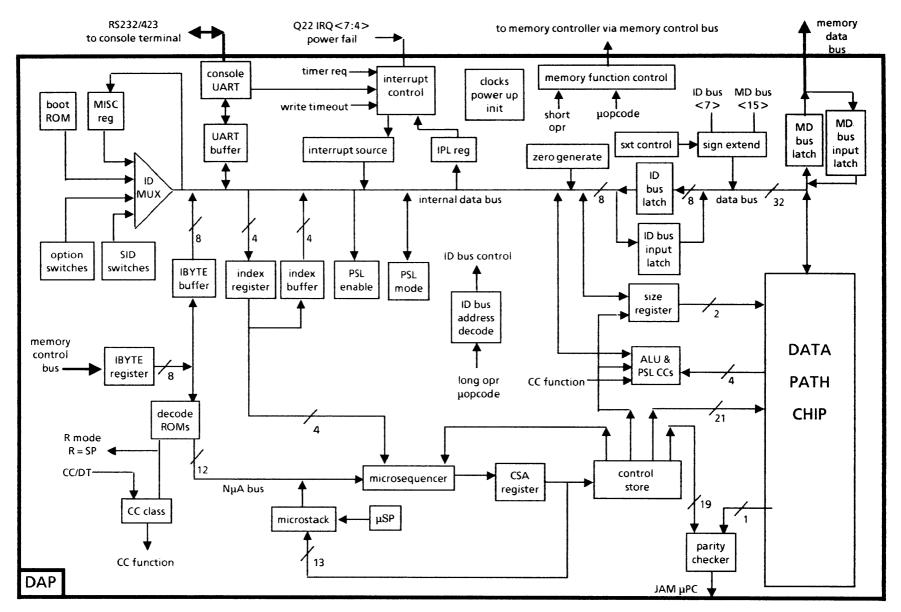

## **Chapter 6: Data Path Module**

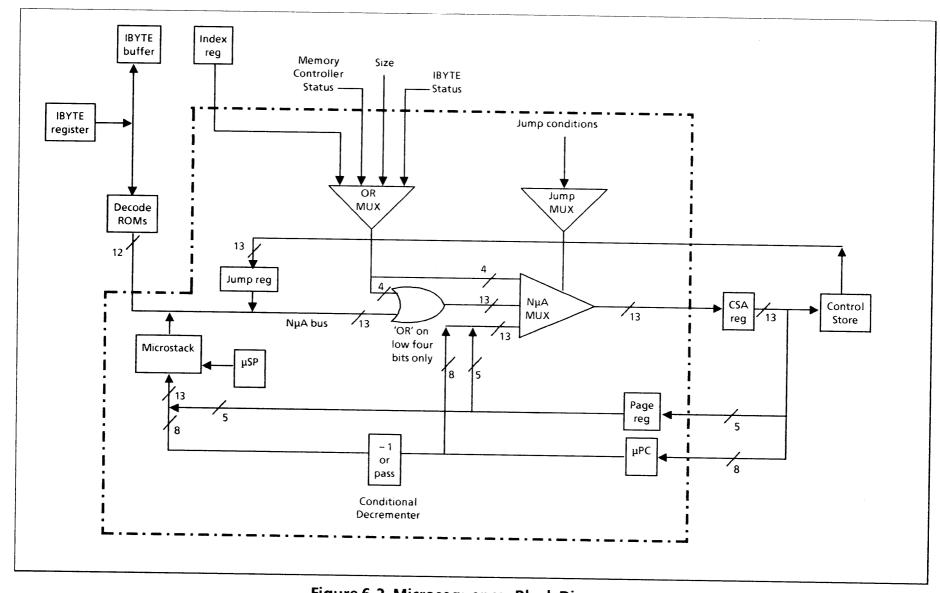

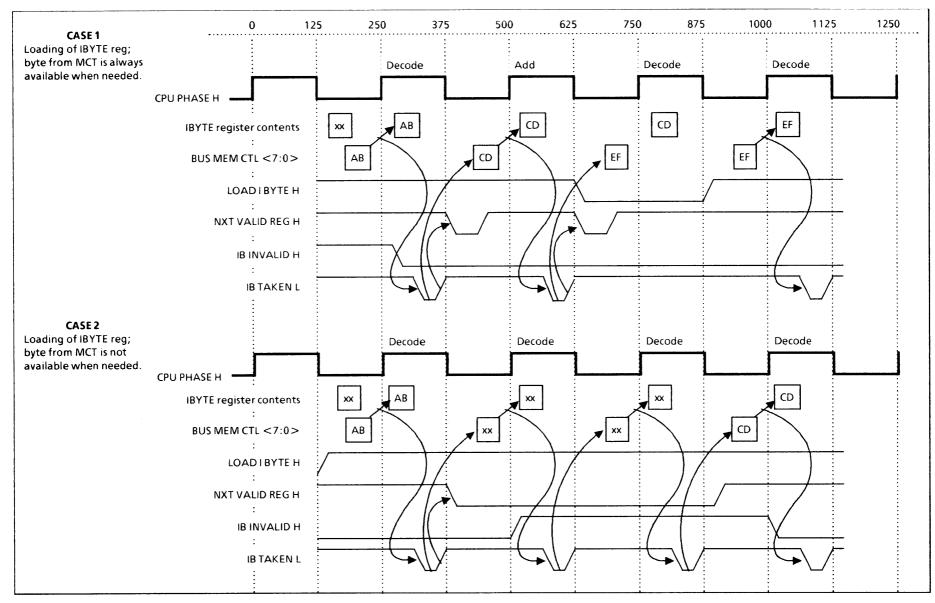

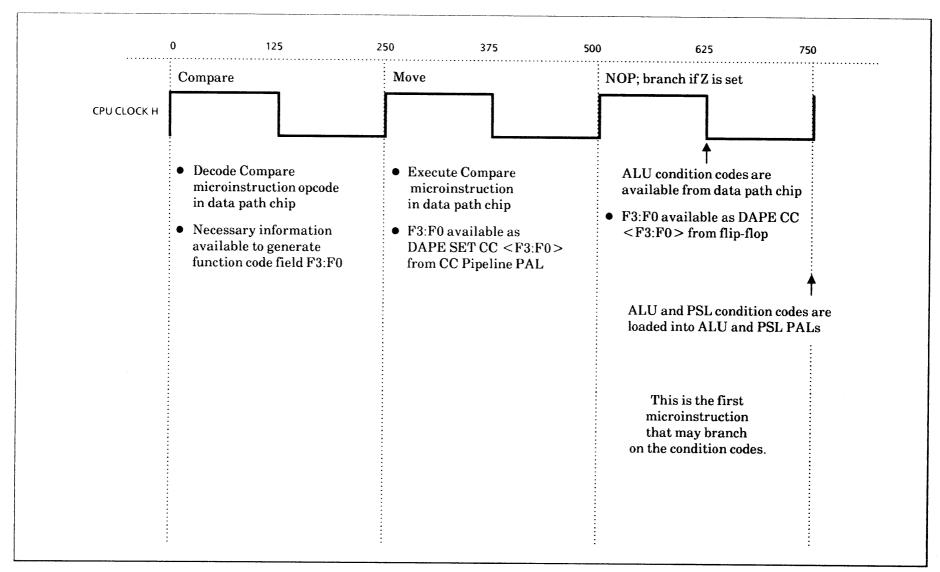

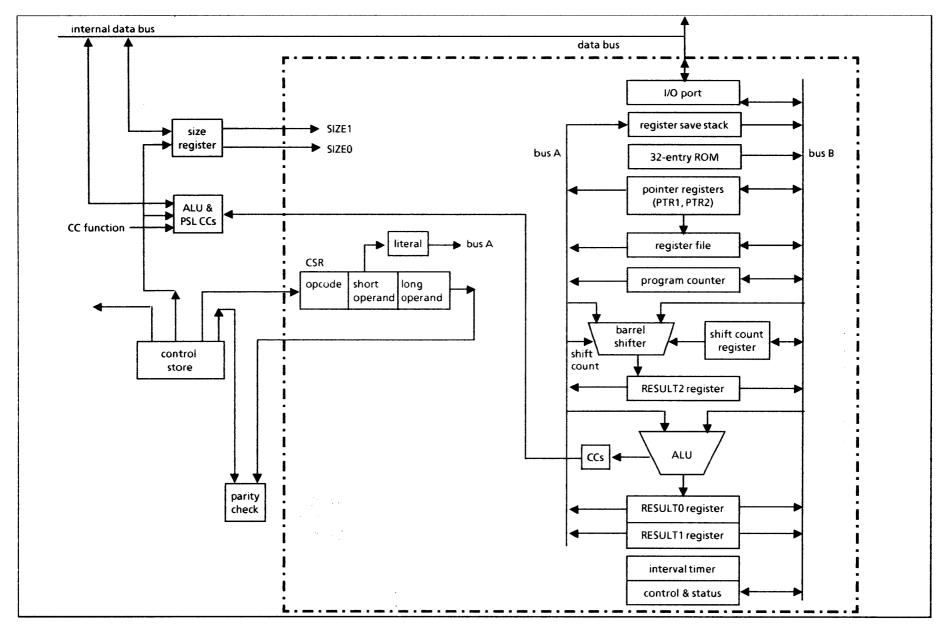

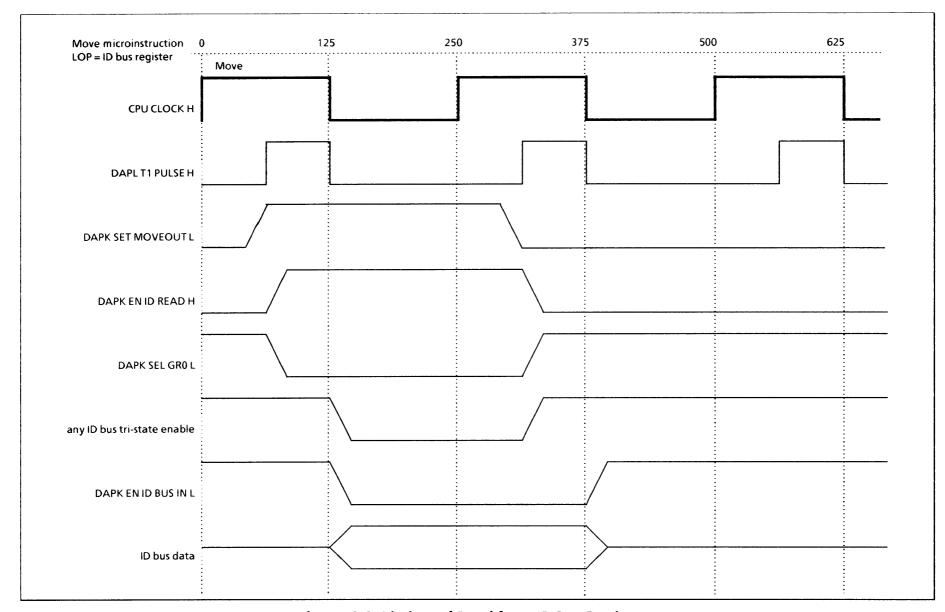

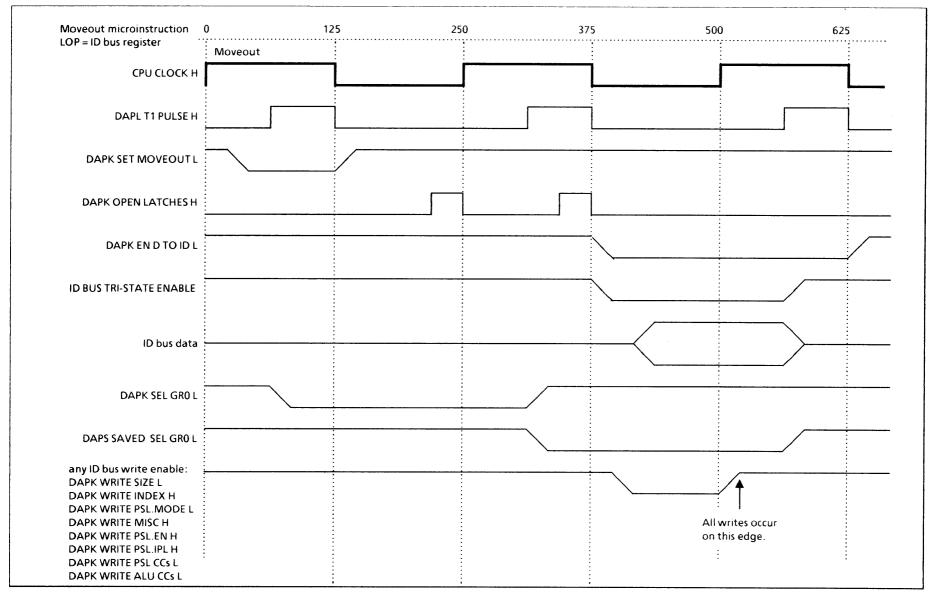

Overview of DAP Functions, 6-1 Controlling the Microinstruction Flow, 6-2 Clock Signals, 6-2 Control Store, 6-5 Control Store Address Register, 6-7 Parity Checker, 6-7 Index Register, 6-8 Microsequencer, 6-8 Page Register and Microprogram Counter, 6-11 Conditional Decrementer, 6-11 Microstack, 6-11 Microstack Pointer, 6-12 Jump Register, 6-13 OR MUX, 6-13 Jump MUX, 6-14 Next Microaddress MUX, 6-15 Decoding Macroinstructions, 6-21 **IBYTE Register, 6-21**

IBYTE Control, 6-22 Decode ROMs, 6-27 ALU and PSL Condition Codes, 6-28 Condition Code Control, 6-29 Condition Code Class Register, 6-29 Condition Code PALs, 6-30 Macrolevel Branch Control, 6-35 PSL Enable, 6-36 Size Register, 6-36 Executing Microinstructions, 6-38 Clock Signal, 6-38 Control Store Register, 6-43 Parity Generator, 6-43 Size Control, 6-43 Data Path Chip Buses, 6-45 Arithmetic and Logic Unit, 6-46 Barrel Shifter, 6-46 Register File, 6-47 Program Counter, 6-51 Result Registers, 6-51 ROM, 6-52 Register Save Stack, 6-52 Pointer Registers, 6-52 Shift Count Register, 6-53 Interval Timer and TMRCSR, 6-53 Condition Codes, 6-54 I/O Port, 6-55 Transferring Data, 6-59 Internal Data Bus, 6-59 Data Bus, 6-60 Sign-Extension, 6-60 ID Bus Latch, 6-61 ID MUX, 6-61 IBYTE Buffer, 6-61 Miscellaneous Register, 6-62

ID Bus Address Decode Logic, 6-63

Zero-Generator, 6-67 Processing Interrupts, 6-67 IPL Register, 6-67 Interrupt Control Logic, 6-68 Priority Encoder, 6-68 Interrupt Source Register, 6-69 Communicating with the Console Terminal, 6-70 Console UART, 6-71 Console UART Registers, 6-71 UART Data Register, 6-72 UART Status Register, 6-73 UART Mode Registers, 6-74 UART Command Register, 6-75 Initializing the UART, 6-76 UART Buffer, 6-76 Option Switches, 6-76 12 Volt Generator, 6-78 Break and Halt Detection, 6-78 Powering Up, 6-80 Power Up Signals, 6-80 Power Failure, 6-81 Initialization State, 6-85 Initialization Signals on Power Up, 6-85 Option Switches, 6-89 Boot EPROM, 6-89 Communicating with the MCT, 6-90 Data Interface, 6-91 Control Interface, 6-92 Interface Control Signals, 6-92 Stalls, 6-93 MD Bus Latches, 6-94 Memory Function Latches, 6-95 Memory Function Control, 6-96 PSL.MODE Register, 6-98 Sign-Extenders, 6-99 Memory Request Timing, 6-100

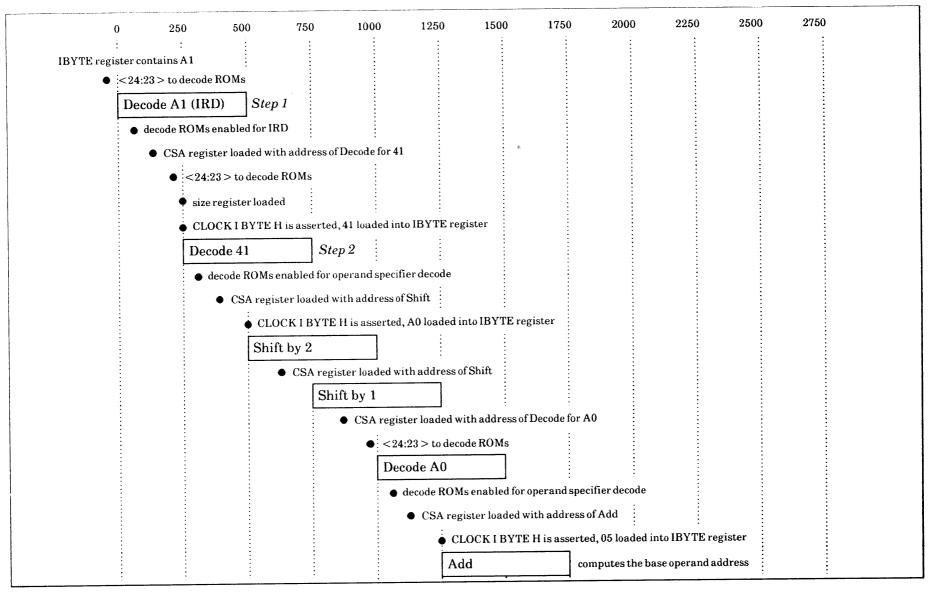

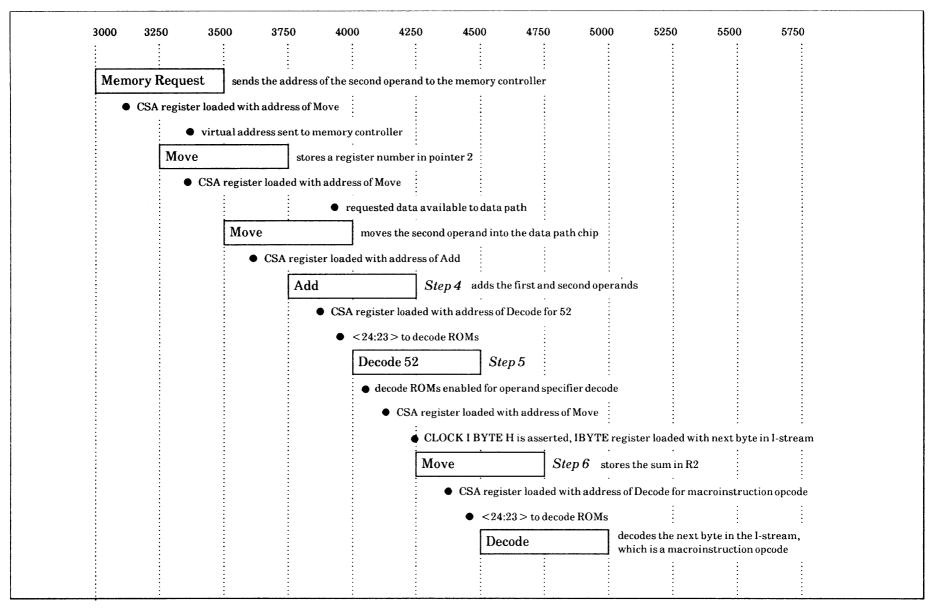

Microprogram Level Flow: ADDW3, 6-105 Evaluating the Opcode: Decode A1, 6-107 Evaluating the First Operand Specifier, 6-109 Decode 41, 6-109 Shift by 2, 6-110 Shift by 1, 6-112 Decode A0, 6-113 Add, 6-114 Move, 6-116 Add, 6-117 Memory Request, 6-117 Move, 6-119 Move, 6-120 Evaluating the Second Operand Specifier, 6-121 Decode 65, 6-121 Memory Request, 6-122 Move, 6-124 Move, 6-125 Adding the Operands, 6-126 Add, 6-126

## **Chapter 7: Memory Controller Microcode**

Decode 52, 6-127 Move, 6-129

Memory Controller Function Parameters, 7-1

Microinstruction Format, 7-4

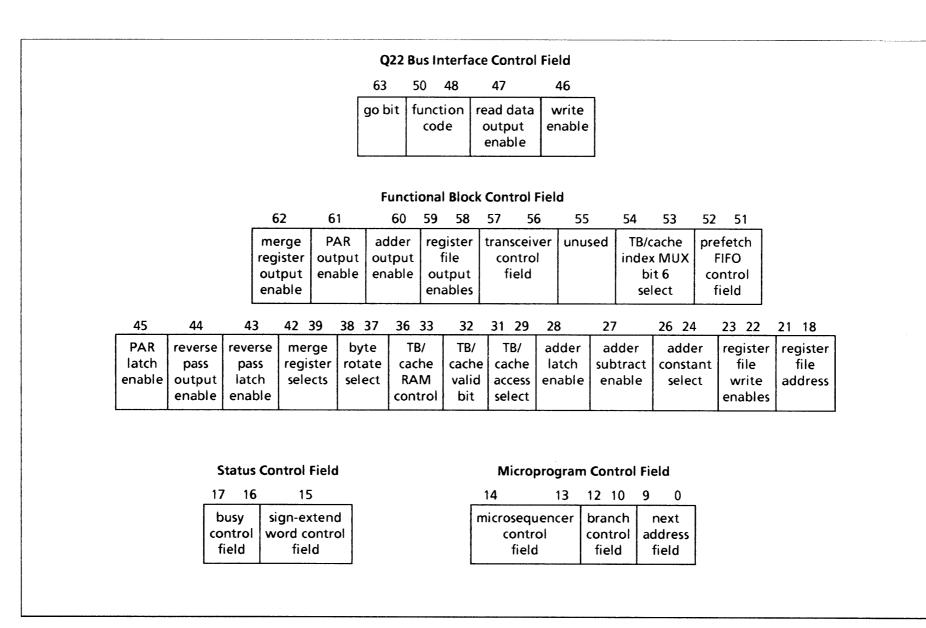

Q22 Bus Interface Control Field, 7-9

Q22 Bus Go Bit, 7-9

Q22 Bus Function Code, 7-10

Q22 Bus Read Data Output Enable, 7-10

Q22 Bus Write Enable, 7-11

Functional Block Control Field, 7-11

Rotate/Merge Block Control, 7-11

Physical Address Register Control, 7-14

Adder Logic Control, 7-15

Register File Control, 7-20

TB/Cache Control, 7-20

Prefetch FIFO Control, 7-24

Reverse Pass Latch Control, 7-24

Status Control Field, 7-25

Busy Control, 7-25

Sign-Extend Word Control Field, 7-26

Microprogram Control Field, 7-27

Microsequencer Control, 7-27

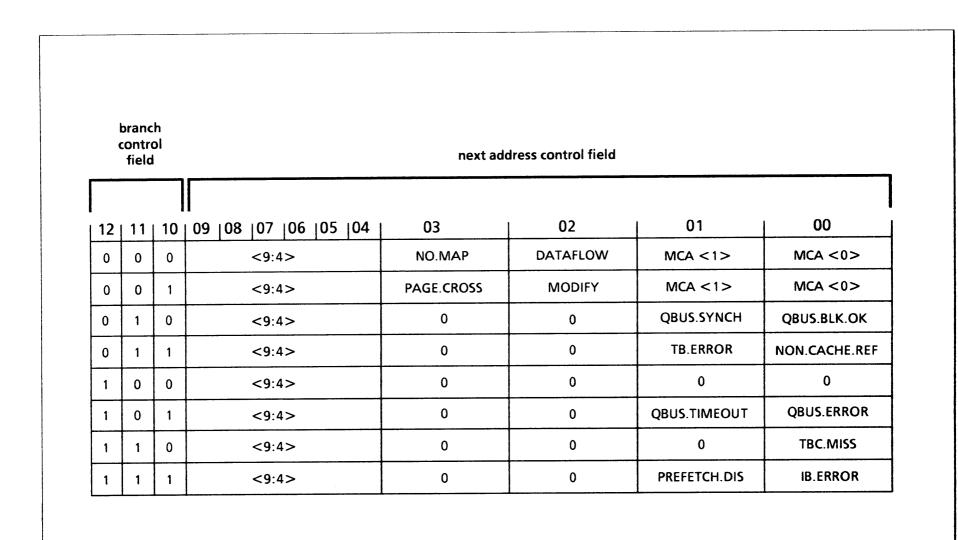

Branch Control, 7-28

Next Address, 7-28

Branch Conditions, 7-29

NO.MAP, 7-33

DATAFLOW, 7-33

MCA < 1 > and MCA < 0 > 7-33

PAGE.CROSS, 7-34

**MODIFY**, 7-34

QBUS.SYNCH, 7-34

QBUS.BLK.OK, 7-34

TB.ERROR, 7-35

NON.CACHE.REF, 7-35

QBUS.TIMEOUT, 7-36

QBUS.ERROR, 7-36

**TBC.MISS, 7-36**

PREFETCH.DIS, 7-36

IB.ERROR, 7-36

Q22 Bus Controller Interface, 7-37

Interface Microcode, 7-37

Q22 Bus Controller Status, 7-38

## **Chapter 8: Memory Controller Module**

Overview of MCT Functions, 8-1

Generating the Clock Signals, 8-2

MCT Clocks, 8-2

Timing, 8-5

Controlling the MCT Microinstruction Flow, 8-6

Memory Request Latch, 8-6

CSA Bus, 8-7

Pull-up Resistors, 8-7 MCT Control Store, 8-7

Microinstruction Clock Gating, 8-8

Branch Condition Logic, 8-8

MCT Microsequencer, 8-9

Microinstruction Decode Logic, 8-10

**CSA PAL, 8-14**

Save Address Register, 8-15

Next Address Buffer and Latch, 8-15

Branch MUX, 8-15

Translating Virtual Addresses, 8-16

Index MUX, 8-16

Tag MUX, 8-17

Tag RAM, 8-18

TB/Cache RAM, 8-20

Write Isolation Buffer, 8-22

TB/Cache Comparator, 8-22

Physical Address Register, 8-23

Register File, 8-23

Adder and Adder Register, 8-25

Translation Buffer Operations, 8-25

Address Sources, 8-25

TB Reads, 8-26

TB Writes, 8-26

TB Invalidates, 8-27

Accessing the Cache, 8-27

Index MUX, 8-28

Tag MUX, 8-28

Tag RAM, 8-29

TB/Cache RAM, 8-30

Write Isolation Buffer, 8-31

TB/Cache Comparator, 8-31

Cache Operations, 8-31

Address Sources, 8-31

Cache Reads, 8-32

Cache Writes, 8-32

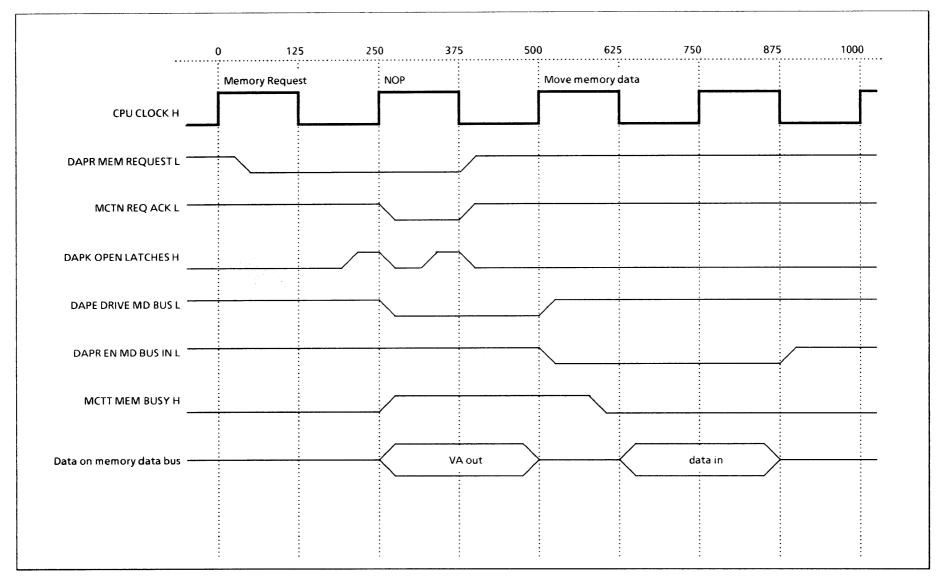

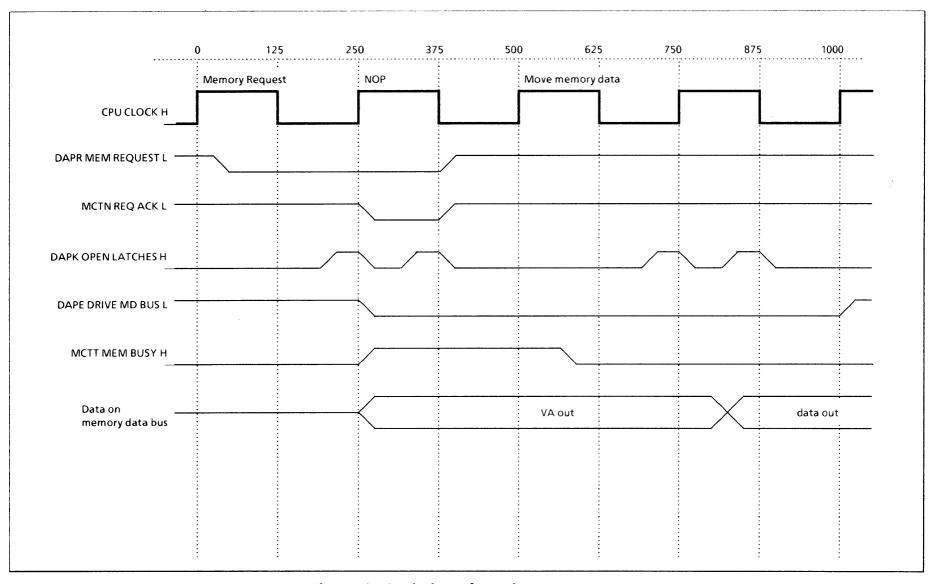

Conditional Cache Invalidates, 8-33 Transferring Data, 8-34 MCA Bus, 8-34 MCD Bus, 8-35 Memory Data Bus Transceiver, 8-36 Memory Control Bus, 8-37 Merge Register and Rotate Logic, 8-37 Reverse Pass Latch, 8-38 Prefetching Instruction Stream Bytes, 8-38 Prefetch FIFO, 8-38 Prefetch FIFO Control Logic, 8-39 Prefetch Program Counter, 8-39 Prefetch Operation, 8-40 Tracking and Reporting Status, 8-41 Control and Status Registers, 8-41 Map Enable Control Register, 8-42 Cache Enable Control Register, 8-42 Error Flag Status Register, 8-42 Instruction Prefetch Error Status Register, 8-43 Access Protection Latch, 8-44 Access Violation PAL, 8-44 Busy Control Logic, 8-49 Sign-Extend Word Flag, 8-50 Communicating with the Q22 Bus Interface, 8-51 O22 Bus Controller, 8-52 Q22 Bus Write Register, 8-52 Q22 Bus Read Register, 8-53 Microprogram Level Flow: MOVW, 8-53 Evaluating the Opcode, 8-55 Evaluating the First Operand Specifier, 8-55 Obtaining the Operand, 8-58 TB Access, 8-59 Cache Access, 8-60 Q22 Bus NOP, 8-62 Set Error Code, 8-62 Servicing the TB Miss, 8-63

TB Write, 8-65

TB Access Retried, 8-70

Cache Access Retried, 8-71

Incorrect Data Returned, 8-73

Q22 Bus Go, 8-73

Read Block, 8-74

Change Q22 Bus Function, 8-75

Read Word, 8-77

Return Correct Data, 8-78

Prepare for Cache Write, 8-79

Cache Write, 8-80

Move Data, 8-81

Evaluating the Second Operand Specifier, 8-81

## **Chapter 9: Q22 Bus Controller**

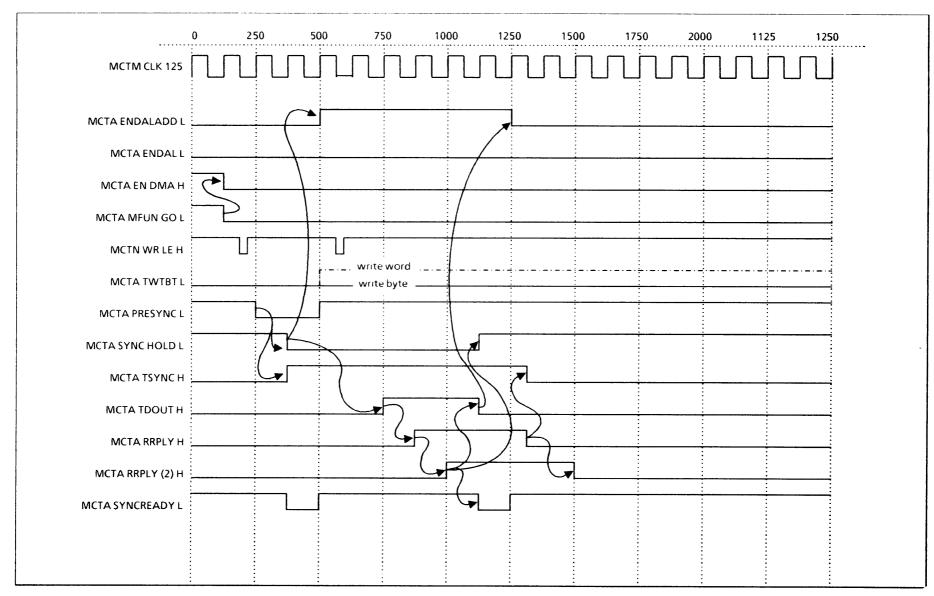

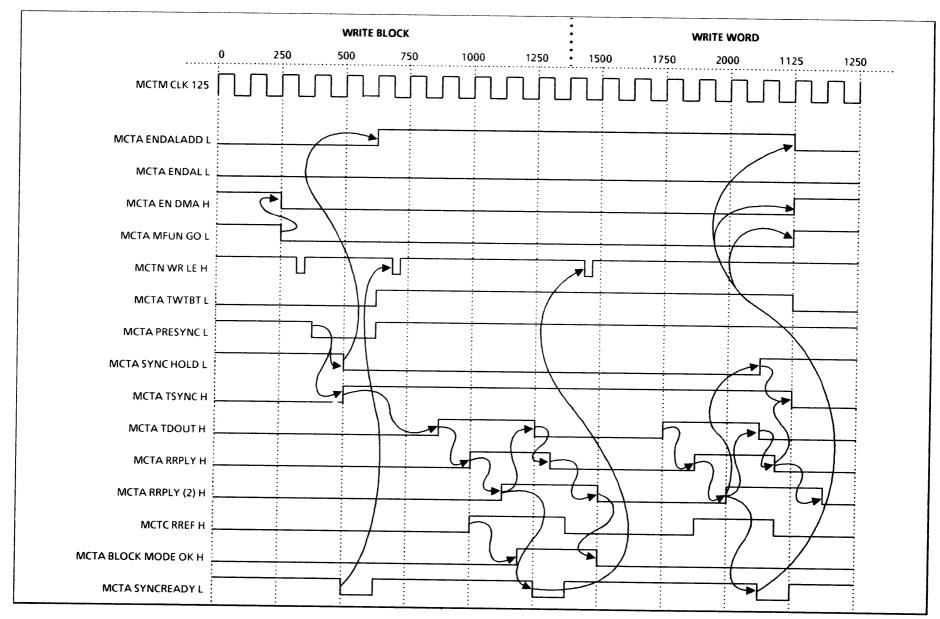

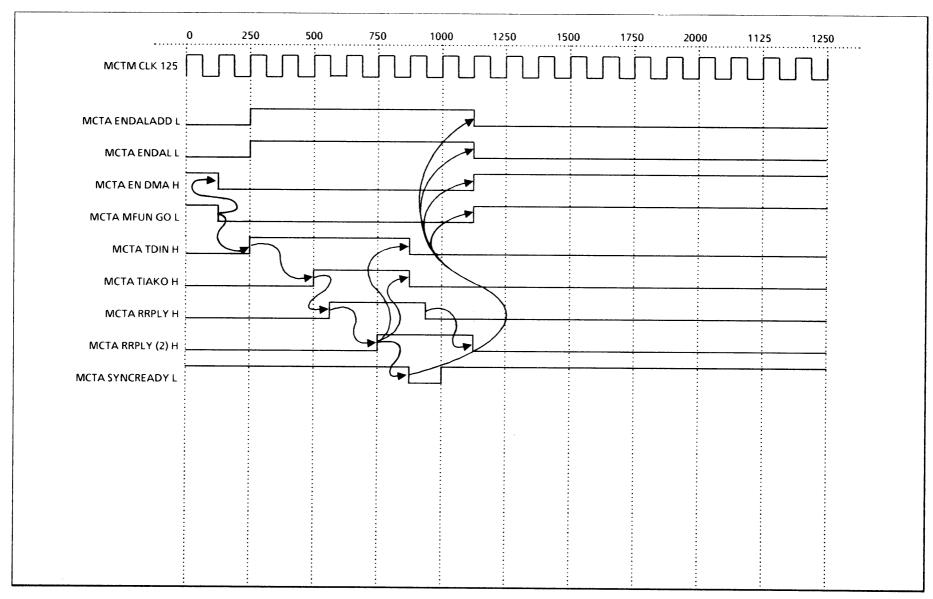

Overview of Q22 Bus Controller Functions, 9-1 Servicing MCT Function Requests, 9-2 Function Decoder PAL, 9-4 Sequencer PAL, 9-5 Q22 Bus Interface, 9-6 Cache Invalidate Pipeline Register, 9-7 O22 Bus Transceivers, 9-7 Sequencing Bus Cycles, 9-8 ENDAL and ENDALADD, 9-8 PRESYNC, 9-9 SYNC HOLD, 9-9 TDIN, 9-10 **TDOUT, 9-10** TWTBT, 9-10 BM TBS7, 9-11 EN IAKO, 9-11 Arbitrating the Q22 Bus, 9-11 Function Decoder PAL, 9-12 Bus Error Logic, 9-13 Parity, 9-13 Bus Timeout, 9-14 Monitoring Direct Memory Accesses, 9-15

DMA Cache Invalidates, 9-15 DATIO Cache Invalidates, 9-18 Communicating with MCT and DAP, 9-21 Block Mode, 9-21 SYNCREADY, 9-21 Q22 Bus Timeout, 9-22 Q22 Bus Error, 9-23 Cache Invalidate, 9-23 Write Timeout, 9-23 Q22 Bus Operations, 9-24 Q22 Bus Signals, 9-24 Master/Slave Relationship, 9-25 Read Word, 9-26 Read Block, 9-31 Write Byte and Write Word, 9-35 Write Block, 9-41 Read Interlocked, 9-45

Appendix A: Q22 Bus Signals, A-1

Read Interrupt Vector, 9-46

Appendix B: Module Finger Pin Assignments, B-1

Appendix C: Serial Line Cable Pinning, C-1

Appendix D: Microverify, D-1

Appendix E: MicroVAX Instruction Set, E-1

Glossary

Index

## **List of Figures**

Figure 1-1. MicroVAX I System, 1-3 Figure 1-2. MicroVAX I Front Panel, 1-9 Figure 1-3. MicroVAX I Backplane, 1-12 Figure 1-4. Microinstruction Timing, 1-19 Figure 2-1. MicroVAX I Physical Memory, 2-2 Figure 2-2. System Virtual to Physical Translation, 2-4 P0 Virtual to Physical Translation, 2-5 Figure 2-3. Figure 2-4. P1 Virtual to Physical Translation, 2-6 Figure 2-5. Bootblock Format, 2-29 Figure 2-6. Bootstrap Flowchart, 2-30 Figure 2-7. Secondary Bootstrap Argument List, 2-36 Memory Layout for Secondary Bootstrap, 2-37 Figure 2-8. Restart Parameter Block, 2-38 Figure 2-9. Figure 2-10. Location of LEDs and Microverify Jumper on Data Path Module, 2-45 Figure 2-11. Machine Check Stack, 2-62 Figure 3-1. Location of Switch Packs on Data Path Module, 3-3 Figure 3-2. Three Types of DIP Switches, 3-11 Figure 4-1. CPU Block Diagram, 4-3 Figure 4-2. Prefetch Operation Data Flow, 4-13 Figure 4-3. MOVB Macroinstruction Data Flow, 4-19 SOBGTR Macroinstruction Data Flow, 4-25 Figure 4-4. Figure 5-1. DAP Microinstruction Format, 5-1 Figure 5-2. Data Path Control Field, 5-4 Next Address Control Field Formats, 5-11 Figure 5-3. Memory Request Format, 5-30 Figure 5-4. Data Path Block Diagram, 6-3 Figure 6-1. Microsequencer Block Diagram, 6-9 Figure 6-2. Next Microaddress Sources, 6-19 Figure 6-3. Figure 6-4. **IBYTE Register Loading, 6-25** Condition Code Setting Timing Diagram, 6-33 Figure 6-5. Figure 6-6. Data Path Chip Block Diagram, 6-41 Data Path Chip Timing Diagram, 6-42 Figure 6-7. Figure 6-8. Timing of Read from ID Bus Register, 6-65 Timing of Write to ID Bus Register, 6-66 Figure 6-9. Power Up/Power Down Timing, 6-83 Figure 6-10.

DAP Initialization Signals, 6-87

Figure 6-12. Timing of a Read from Memory, 6-101 Figure 6-13. Timing of a Write to Memory, 6-102

Figure 6-11.

- Figure 6-14. ADDW3 Microinstructions, 6-131

- Figure 7-1. MCT Microaddress, 7-3

- Figure 7-2. MCT Microinstruction, 7-7

- Figure 7-3. Branch Control Field and Next Address Field Formats, 7-31

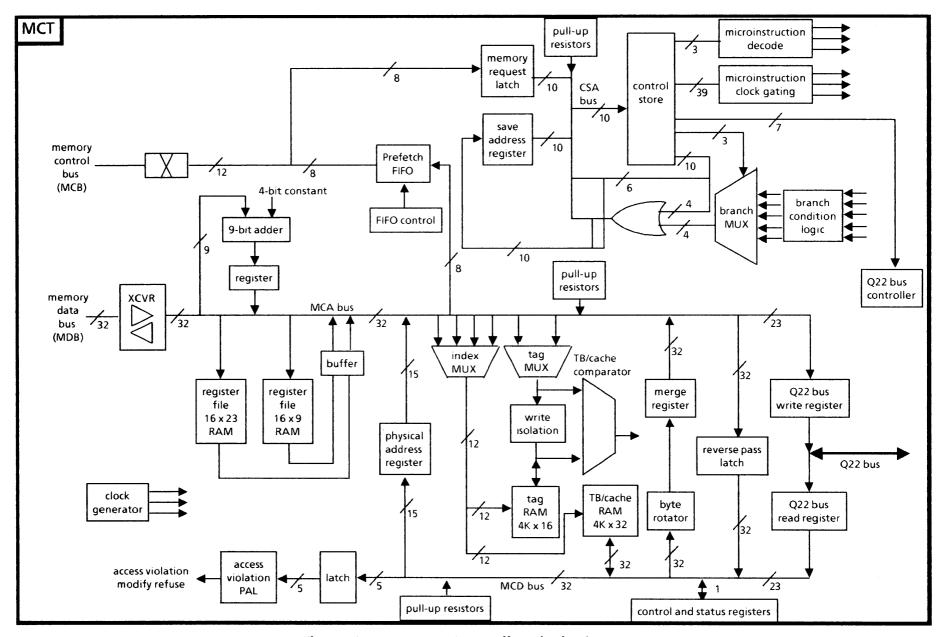

- Figure 8-1. Memory Controller Block Diagram, 8-3

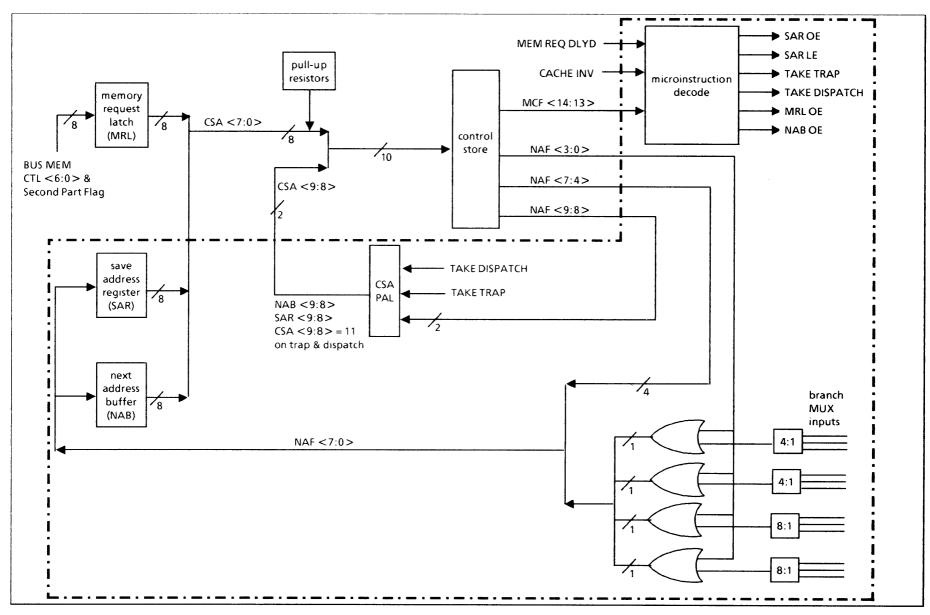

- Figure 8-2. MCT Microsequencer Block Diagram, 8-11

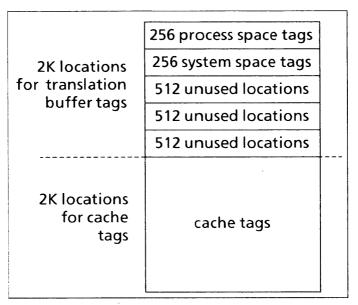

- Figure 8-3. Organization of Tag RAM, 8-19

- Figure 8-4. Translation Buffer Tag, 8-19

- Figure 8-5. Organization of TB/cache RAM, 8-21

- Figure 8-6. Translation Buffer PTE, 8-21

- Figure 8-7. Cache Tag, 8-29

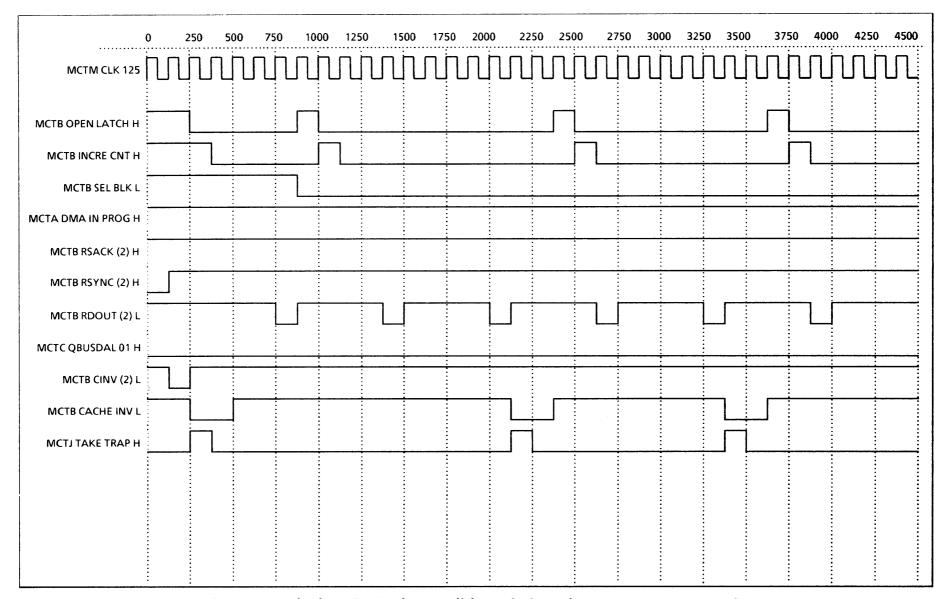

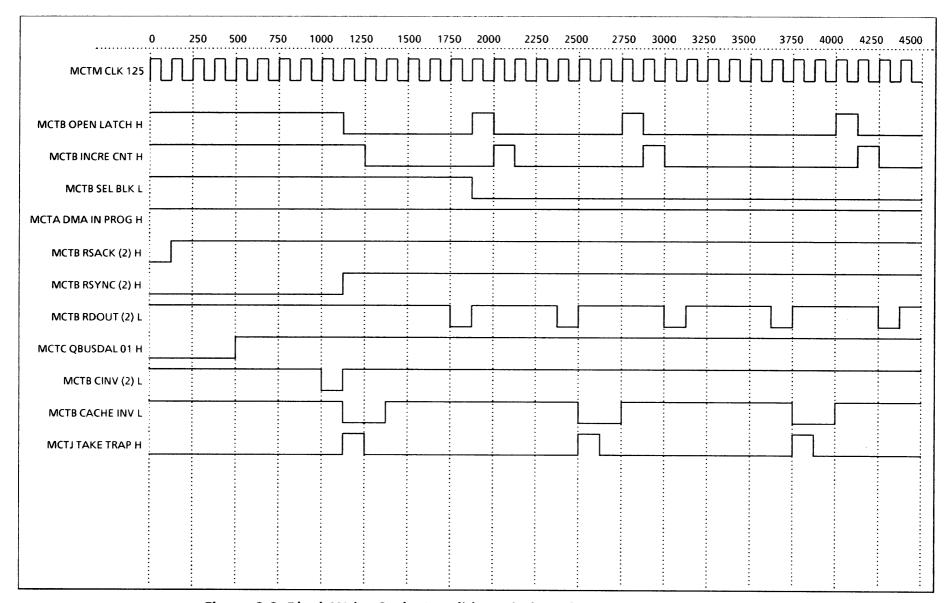

- Figure 9-1. Block Write Cache Invalidate Timing Diagram: BDAL < 1 > = 0, 9-19

- Figure 9-2. Block Write Cache Invalidate Timing Diagram: BDAL < 1 > = 1, 9-20

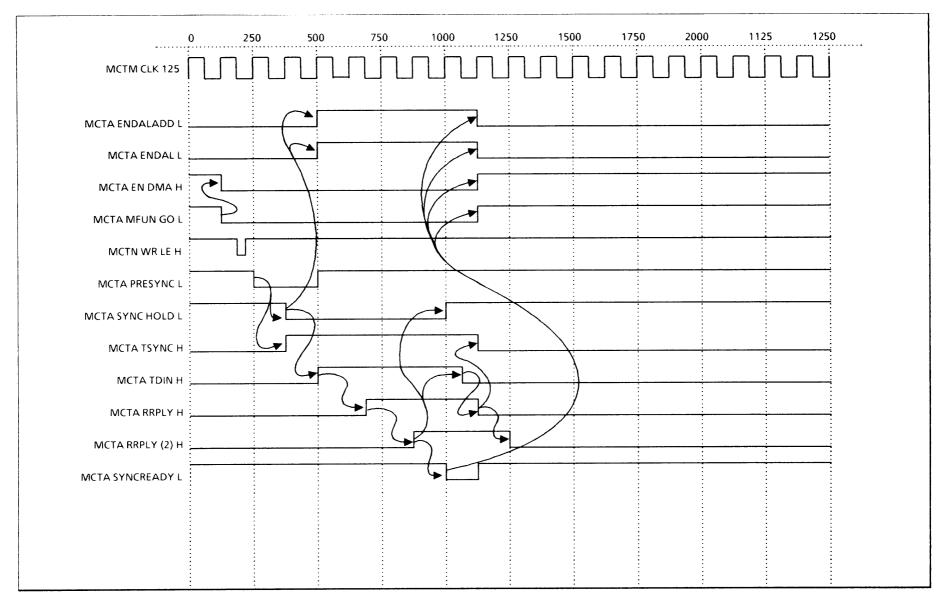

- Figure 9-3. Read Word Timing Diagram, 9-29

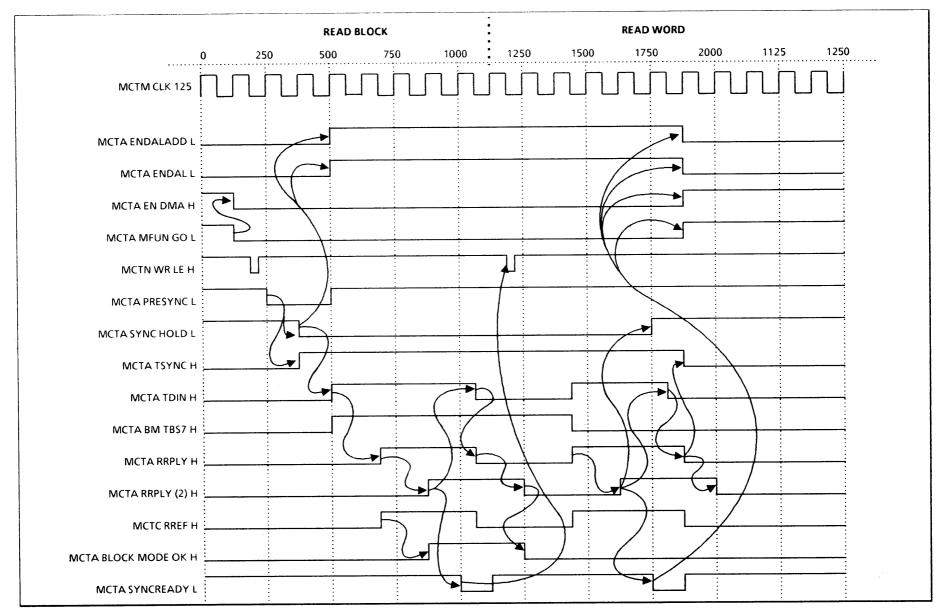

- Figure 9-4. Read Block Timing Diagram, 9-33

- Figure 9-5. Write Byte/Write Word Timing Diagram, 9-39

- Figure 9-6. Write Block Timing Diagram, 9-43

- Figure 9-7. Read Interrupt Vector Timing Diagram, 9-49

## **List of Tables**

- Table 1-1. Front Panel Switches, 1-9

- Table 1-2. Front Panel Indicators, 1-9

- Table 2-1. Internal Processor Registers, 2-9

- Table 2-2. TXDB Register Encoding, 2-19

- Table 2-3. Device Names, 2-23

- Table 2-4. Boot Command Flags, 2-24

- Table 2-5. LEDs and Patch Panel Display, 2-42

- Table 2-6. Console Halt Codes, 2-49

- Table 2-7. Interrupt Priority Levels, 2-53

- Table 2-8. Arithmetic Traps/Faults, 2-55

- Table 2-9. Machine Checks, 2-65

- Table 2-10. System Control Block Organization, 2-71

- Table 3-1. Option Switch Settings, 3-5

Table 3-2. Processor Temperature Specifications, 3-15 Condition Code Field Encoding, 5-3 Table 5-1. Data Type Field Encoding, 5-3 Table 5-2. Table 5-3. Operand Specifier Decodes: CC/DT Field Encoding, 5-4 Table 5-4. Opcode Assignments, 5-7 Jump Control Field, 5-11 Table 5-5. Table 5-6. OR <2:0>, 5-11 Table 5-7. Decode Microinstruction Short Operand, 5-20 Table 5-8. Register Address Organization, 5-27 Table 5-9. Read MCT Function Codes, 5-42 Table 5-10. Write MCT Function Codes, 5-43 Table 6-1. Forced Zeros on NuA MUX Output, 6-17 Table 6-2. Condition Code Class Register Encoding, 6-30 CC Function Field Encoding, 6-31 Table 6-3. Table 6-4. Barrel Shifter Functions, 6-47 DPC Registers, 6-49 Table 6-5. Table 6-6. Data Path Chip Condition Codes, 6-55 Table 6-7. External Registers, 6-57 Table 6-8. Interrupt Source Register Encoding, 6-70 Table 6-9. UART Registers, 6-72 Table 6-10. DAP/MCT Interface Signals, 6-103 Table 7-1. Function Code Field, 7-10 Table 7-2. Merge Register Selects, 7-13 Byte Rotate Select, 7-13 Table 7-3. Table 7-4. Adder Control, 7-16 Table 7-5. Register File Address Space, 7-19 Table 7-6. Transceiver Control Field, 7-20 Table 7-7. Index MUX <6> Select, 7-21 Table 7-8. TB/Cache RAM Control, 7-22 Table 7-9. TB/Cache Access Select, 7-23 Table 7-10. Busy Control Field Encoding, 7-26 Table 7-11. Microsequencer Control Field Encoding, 7-27 MCA Bus Sources, 8-35 Table 8-1. Table 8-2. MCA Bus Destinations, 8-35

MCD Bus Sources, 8-36

Table 8-3.

Table 8-4. MCD Bus Destinations, 8-36

Table 8-5. MCT Error Codes, 8-43

Table 8-6. Protection Codes, 8-47

Table 9-1. Function Code Field, 9-3

## **Preface**

## **Manual Scope**

This manual is a technical description of the central processing unit (CPU) used in the MicroVAX I system. The MicroVAX I can have either the KD32-AA CPU (F\_ and G\_floating point) or the KD32-AB CPU (F\_ and D\_floating point). Both processors consist of two quadheight modules:

- The data path module (M7135 for the KD32-AA CPU, M7135-YA for the KD32-AB CPU), and

- The memory controller module (M7136).

This technical description is intended as a field reference for DIGITAL Field Service personnel and a resource for training programs conducted by Educational Services and Manufacturing. A knowledge of VAX architecture is assumed.

Chapter 1 is a general description of the MicroVAX I system.

The next two chapters comprise a user's guide for the KD32-AA and KD32-AB processors. Chapter 2, "Programming Interface," contains information a MicroVAX I programmer needs to know such as the system physical address space, the macrolevel registers, the boot EPROM, and machine checks. Chapter 3, "Module Configuration," describes the factory configuration of the processor and how to change it, plus power and cooling specifications.

Beginning with Chapter 4, the remaining chapters provide a "theory of operation" description of the

processor modules. Chapter 4 is a functional overview of the CPU, Chapters 5 and 6 describe the data path module microcode and hardware, Chapters 7 and 8 describe the memory controller module microcode and hardware, and Chapter 9 describes the Q22 bus controller.

The MicroVAX I Field Service Print Set, MP-01896-01, contains schematic diagrams for the processor modules. Signal names in the MicroVAX I CPU Technical Description are prefaced by four-letter codes which reference pages in the Print Set. You may find it helpful to refer to the Print Set as you read the Technical Description.

## **Related Documentation**

The *MicroVAX I CPU Technical Description* is part of the hardware documentation set for the MicroVAX I system. Related manuals that may be of interest are:

- MicroVAX I Owner's Manual, EK-KD32A-OM.

This book contains installation, operation, diagnostics, troubleshooting, removal and replacement procedures, and system configuration information for the MicroVAX I system.

- MicroVAX Handbook, EB-25156-47. This book contains descriptions of the MicroVAX I system and related products: peripherals, interfaces, operating systems, and communications software.

- VAX Architecture Handbook, EB-19580-20. The MicroVAX I system design is based on the VAX architecture described in this handbook.

- Microcomputer Interfaces Handbook, EB-20175-20. This handbook is a reference guide for the interface and peripheral hardware options that can be

- installed on the Extended LSI-11 Bus used in the MicroVAX I system.

- Microcomputers and Memories, EB-20912-20. This manual contains a detailed description of the Extended LSI-11 Bus.

## Chapter 1 Introduction

This chapter introduces the MicroVAX I system. It contains information about the system necessary for understanding the MicroVAX I central processing unit (CPU).

## **System Overview**

The MicroVAX I system is a 32-bit, high-performance, microprogrammed computer. The processor executes the VAX-11 instruction set and contains an interface to the extended LSI-11 bus (Q22 bus). PDP-11 compatibility mode is not supported.

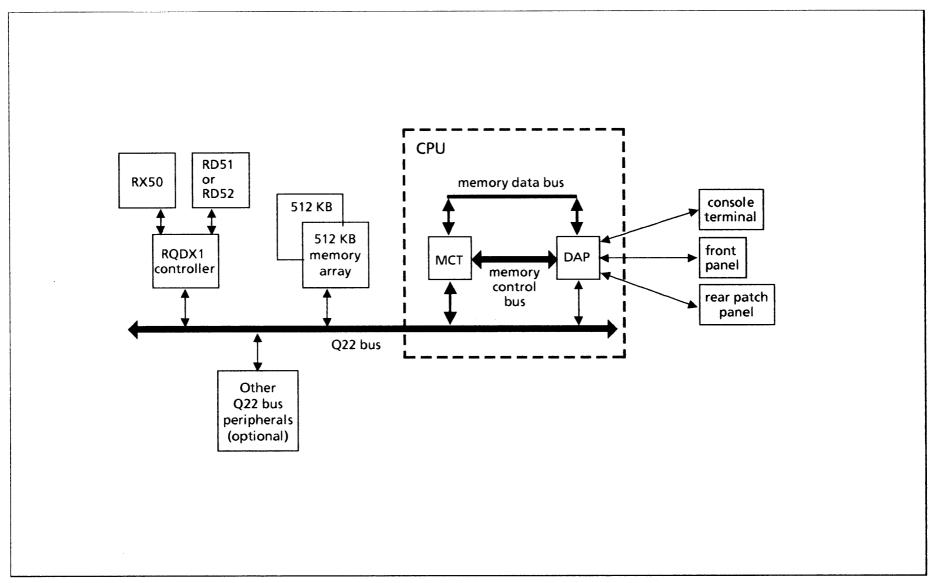

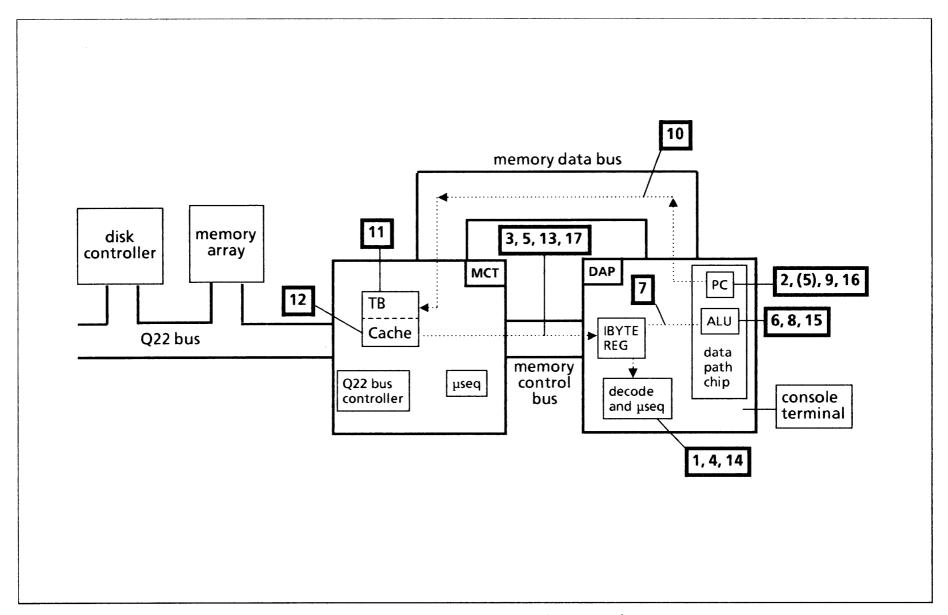

The major components of the MicroVAX I system, shown in Figure 1-1, are:

- The processor, which consists of two modules:

- data path module (DAP)

- memory controller module (MCT)

- Q22 bus

- RQDX1 controller

- RX50 diskette drives

- RD51 or RD52 fixed disks

- Q22 memory, with block mode capability

- Console terminal

- Front control panel

- Rear patch panel assembly

The Q22 bus-compatible system box also contains a backplane and power supply.

#### **Processor**

The processor consists of two quad-height modules and contains:

- An interface to the Q22 bus which supports block mode transfers and up to four megabytes of physical memory

- An 8 KB direct-mapped cache

- A 512 entry (longword) translation buffer

- A 10 ms nonprogrammable interval timer

- An interface to a console serial line unit

- An 8 KB or 16 KB boot EPROM

- Interfaces to the front control panel and rear patch panel assembly.

Two processors are available for the MicroVAX I system. The KD32-AA processor contains microcode to handle  $F_-$  and  $G_-$ floating point instructions. The KD32-AB processor contains microcode to handle  $F_-$  and  $D_-$ floating point instructions.

Figure 1-1. MicroVAX I System

#### Q22 Bus

The MicroVAX I system backplane uses the extended LSI-11 bus (also called the Q22 bus), which has 22-bit addressing. The Q22 bus consists of 42 bidirectional and 2 unidirectional signal lines. These are the lines along which the processor, memory, and I/O devices communicate with each other. MicroVAX I performs the following Q22 bus data transfer functions:

DATI read word

DATO write word

DATOB write byte

DATIO read, modify, write word

DATIOB read, modify, write byte

DATBI read block

DATBO write block

### **RQDX1 Controller**

The RQDX1 controller (M8639) is a quad-height module that occupies the last-used slot in the backplane. It is the interface between the Q22 bus and the RX and RD disk drives. The controller is a direct memory access (DMA) interface and uses mass storage control protocol (MSCP). It also provides support for gather-read and scatter-write operations; that is, transfers do not have to be physically contiguous.

## **RX50 Diskette Drive**

The RX50 is a random access storage device with two diskette drives. It uses single-sided 5.25 inch (13.34 cm) diskettes. The total drive capacity is 800K bytes of formatted data. Each drive has an access door and slot for inserting and removing diskettes. A head load LED

for each diskette slot informs the user when that unit is busy.

The RX50 is a field replaceable unit (FRU) that mounts in the MicroVAX I system box. Cables connect the RX50 to the RQDX1 controller and the power supply. See the *MicroVAX I Owner's Manual* for removal and replacement procedures.

#### **RD51 and RD52 Fixed Disk Drives**

The RD51 is a random access storage device which uses two nonremovable 5.25 inch (13.34 cm) disks as storage media. One movable head per disk surface services 153 data tracks. The total formatted capacity of the four heads and surfaces is 10 megabytes.

The RD52 is a random access storage device which also uses nonremovable 5.25 inch (13.34 cm) disks as storage media. The total formatted capacity of the RD52 is 31 megabytes.

The RD51 and RD52 are field replaceable units (FRUs) that mount in the MicroVAX I system box. A control cable and one data cable connect the RD51 or RD52 drive to the RQDX1 controller. Another cable connects the RD51 or RD52 drive to the power supply. See the *MicroVAX I Owner's Manual* for removal and replacement procedures.

The RD51 is also available as the RD51-D (desk top) or RD51-R (rack mount) disk subsystem. Similarly, the RD52 is available as the RD52-D (desk top) or RD52-R (rack mount) disk subsystem. The RD51-D, RD51-R, RD52-D, and RD52-R are freestanding, outboard fixed disk subsystems that contain their own power, cooling, console, and I/O cable. The RQDX1 controller plus the RQDX1-E bus extender card are the interface between the Q22 bus and the disk subsystem.

#### Memory

MicroVAX I relies on block mode Q22 bus data transfer functions to realize its performance goals. Therefore, MicroVAX I systems are configured with MSV11-P memory modules, which have block mode capability.

The MSV11-P family of memory modules are quadheight modules that implement an 18-bit wide random access memory array (16 data bits and 2 parity bits), parity generation and detection, and on-board refresh circuitry. There are two variations:

MSV11-PL 512 KB of storage using 64K MOS RAMs

MSV11-PK 256 KB of storage using 64K MOS RAMs

#### Console Terminal

The console terminal may be any member of the VT100 or VT200 family of terminals. A cable connects the terminal to an EIA connector on the CPU patch panel, located at the back of the MicroVAX I system box. Appendix C lists the pinout for the EIA connector.

An internal cable attaches the EIA connector on the CPU patch panel to a 10-pin connector on the data path module. A terminal interface UART and an RS232/423 driver and receiver pair are located on the data path module.

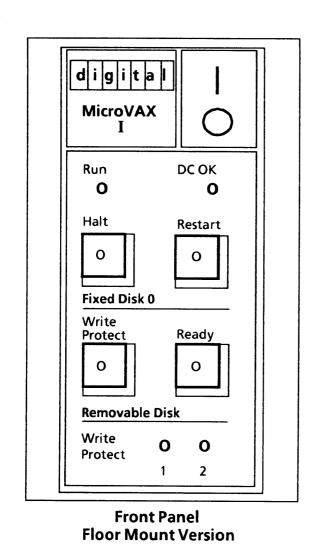

#### **Front Control Panel**

The front panel provides control and status of the various components of the system. The switches and indicators are shown in Figure 1-2. The switches and their functions are listed in Table 1-1. The indicators and their meanings are listed in Table 1-2.

The front control panel is a field replaceable unit (FRU). See the *MicroVAX I Owner's Manual* for removal and replacement procedures.

## **Patch Panel Assembly**

External option cables and serial lines connect to the MicroVAX I through the rear patch panel assembly. The patch panel assembly provides shielding for EMI and accommodates a variety of connectors by providing six areas for patch panel inserts; the connectors are an integral part of the patch panel inserts. The inserts mount in cutouts in the sheet-metal frame of the patch panel assembly. Four screws hold each insert in place. When an area is not occupied by an insert, a metal plate covers the cutout for the insert.

Four of the patch panel areas are  $2\times3$  inches; the other two areas are each  $1\times4$  inches. An alternate configuration can be created by removing the divider post between the third and fourth patch panel areas and installing three  $1\times4$  inch inserts.

The  $2\times3$  inch patch panel areas can each accommodate an insert with four 25-pin EIA connectors. The  $1\times4$  inch areas can each accommodate an insert with one 40-pin or one 50-pin EIA connector.

The insert for the KD32-AA or KD32-AB CPU is installed in the first 2×3 inch patch panel area. This CPU patch panel contains one 25-pin EIA connector, one rotary baud rate select switch, and a two-digit LED display. The rotary switch sets the system baud rate; the choices are 300, 1200, 9600, and 19,200 baud.

**Table 1-1. Front Panel Switches**

| Switch        | Position                    | Function                                                                                                                                               |

|---------------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 0          | 1                           | Turns on the system power.                                                                                                                             |

|               | 0                           | Turns off the system power.                                                                                                                            |

| Halt          | In (LED lit)                | The processor halts and responds to console commands.                                                                                                  |

|               | Out (LED off)               | Enables the processor to run.                                                                                                                          |

| Restart       | In<br>(momentary<br>switch) | When the halt switch is out (LED off), the processor carries out a power-up sequence. When the halt switch is in (LED lit), this button has no effect. |

| Write Protect | In (LED lit)                | Write protects fixed disk 0.                                                                                                                           |

|               | Out (LED off)               | Enables writing to fixed disk 0.                                                                                                                       |

| Ready         | In (LED off)                | Places fixed disk 0 off-line.                                                                                                                          |

|               | Out (LED lit)               | Places fixed disk 0 on-line.                                                                                                                           |

**Table 1-2. Front Panel Indicators**

| LED         | Function                                                                                                              |  |

|-------------|-----------------------------------------------------------------------------------------------------------------------|--|

| Run         | The Run LED is on when the processor is operating; the LED goes off when the processor is not executing instructions. |  |

| DC OK       | This LED is on when the power supply is generating correct DC power output voltages.                                  |  |

| Removable D | Pisk Write Protect                                                                                                    |  |

| 1           | When lit, the diskette in drive 1 is write protected.                                                                 |  |

| 2           | When lit, the diskette in drive 2 is write protected.                                                                 |  |

Figure 1-2. MicroVAX I Front Panel

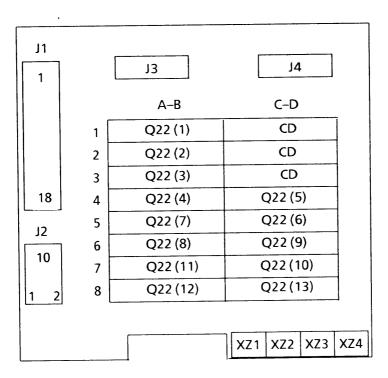

## **Backplane**

The backplane (H9278-A) is a four-row by eight slot backplane capable of accepting either quad- or double-height modules. The backplane uses the Q22 bus structure in the A and B connectors of slots 1 through 8, and in the C and D connectors of slots 4 through 8. A slot-to-slot interconnection scheme (referred to as the CD interconnect) is wired in the C and D connectors of slots 1 through 3. The CD interconnect connects selected side two pins in rows C and D of a given slot to side one pins of the slot immediately following. There are 32 such connections per slot.

The backplane receives and distributes two voltages and ground. Maximum ratings are +5 volts at 36 amps, and +12 volts at 6 amps.

The backplane includes four connectors, J1 through J4, which are mounted on side two of the backplane. J1 (eighteen pins), J3 (four pins), and J4 (four pins), connect power supply outputs to the backplane. J2 (ten pins) connects the backplane to the front panel.

The backplane also includes provision for the insertion of four resistor packs (p/n 1318110-00) into positions XZ1, XZ2, XZ3, and XZ4. In a MicroVAX I system (single backplane), these resistor packs are inserted to terminate the Q22 bus lines. (Characteristic impedance is 220 ohms).

Figure 1-3 shows the backplane organization. The numbers in the parentheses following the Q22 designations show the path of interrupt and direct memory access grant continuity for options installed in the backplane; increasing value denotes lower priority. Each slot requires the insertion of a module or a bus grant continuity card to pass these grant signals on as

no jumpers are provided on the backplane for this purpose.

Figure 1-3. MicroVAX I Backplane

## **Power Supply**

The power supply (H7864) is a modular, 230-watt power supply that supplies from 4.5 amps minimum to 36 amps maximum at +5 volts, and 0 to 7 amps at +12 volts. There are also two outputs designed to accommodate DC brushless fans, not included in the 230-watt power specification. These outputs supply 0.45 amps at +12 volts and +9 volts.

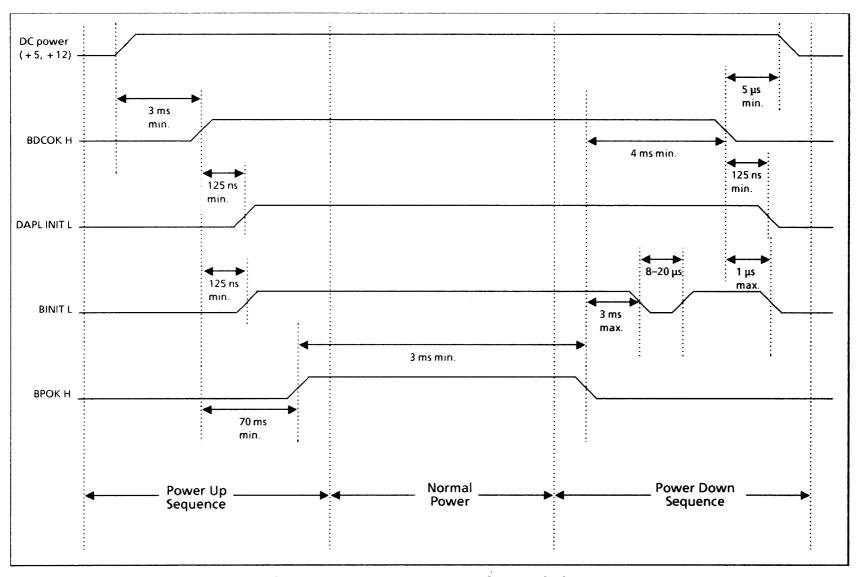

Other power supply features include thermal shut down, overvoltage and overcurrent protection, AC input transient suppression, and three Q22 bus signals (BPOK, BDCOK, BEVNT; see Appendix A for signal definitions). In addition, the power supply has a full cycle ride-through feature; that is, the power supply maintains the output voltages at operating level for a minimum of one 60 Hz cycle if the AC input voltage drops.

The power supply includes connectors that provide the necessary power and signal interfaces to the logic backplane, mass storage units, front panel, and fans.

The power supply is a field replaceable unit (FRU). See the *MicroVAX I Owner's Manual* for removal and replacement procedures.

## **System Architecture**

The VAX architecture is an architecture designed by DIGITAL for its family of 32-bit, virtual memory minicomputers. DIGITAL has also defined a subset of the VAX architecture called the MicroVAX architecture.

## MicroVAX Architecture

The MicroVAX architecture is tailored to facilitate lowend implementations of the VAX family of computers. The features of the MicroVAX architecture are:

- A four gigabyte virtual address space

- 32-bit word size

- Sixteen 32-bit general purpose registers

- 32 interrupt levels

- Vectored hardware and software interrupts

- 21 addressing modes

- Variable instruction size

- Full memory management

- virtual to physical address translation

- page protection mechanism

- Stack processing

- Full VAX instruction set (except PDP-11 compatibility mode)

The MicroVAX architecture specifies a subset of instructions that **must** be implemented in hardware. The remaining instructions may optionally be implemented in hardware, or emulated in software. The instructions that do not have to be implemented in hardware are:

- decimal string instructions

- character string instructions except MOVC3 and MOVC5

- EDITPC or CRC instructions

- D\_floating, F\_floating, G\_floating, and H\_floating instructions.

Thus, any machine implementing the MicroVAX architecture can execute the full VAX instruction set (minus PDP-11 compatibility mode).

For those instructions that do not have to be implemented in hardware, the MicroVAX architecture specifies two kinds of emulation support: instructions emulated strictly in software, and instructions emulated in software with a hardware assist.

The MicroVAX architecture specifies that all floating point instructions (D, F, G, and H) are emulated strictly in software (if they are not implemented in hardware).

The MicroVAX architecture specifies that the following instructions are emulated in software with a hardware assist (if they are not implemented in hardware):

- decimal string: MOVP, CMPP3, CMPP4, ADDP4, ADDP6, SUBP4, SUBP6, MULP, DIVP, ASHP, CVTPL, CVTLP, CVTPS, CVTSP, CVTTP, CVTPT

- character string: MOVTC, MOVTUC, SKPC, LOCC, SCANC, SPANC, MATCHC, CMPC3, CMPC5

- cyclic redundancy check: CRC

• edit: EDITPC

The MicroVAX architecture supports a subset of VAX processor registers. The following internal processor registers (IPRs) are either not required by the MicroVAX architecture, or are specified differently by MicroVAX architecture:

| ICCS  | interval clock control/status<br>register |

|-------|-------------------------------------------|

| NICR  | next interval count register              |

| ICR   | interval count register                   |

| TODR  | time of year register                     |

| RXCS  | console receive control status            |

| RXDB  | console receive data buffer               |

| TXCS  | console transmit control status           |

| TXDB  | console transmit data buffer              |

| TBIS  | translation buffer invalidate single      |

| PMR   | performance monitor enable                |

| TBCHK | translation buffer check                  |

#### MicroVAX I Implementation

The MicroVAX I system implements a superset of the MicroVAX architecture in that it implements more than the specified subset of instructions in hardware, and implements some IPRs not required by the MicroVAX architecture. The differences between the MicroVAX architecture, and the MicroVAX I implementation of it, are as follows.

- The MicroVAX architecture specifies emulation support for the following character string and floating point instructions, whereas MicroVAX I implements them in hardware:

- CMPC3

- LOCC

- SCANC

- SKPC

- SPANC

- F\_floating point instructions

- G\_floating point instructions (KD32-AA CPU)

- D\_floating point instructions (KD32-AB CPU)

- The MicroVAX architecture does not specify the implementation of the following six IPRs. MicroVAX I implements them as defined by the VAX architecture:

| RXCS | console receive control status       |

|------|--------------------------------------|

| RXDB | console receive data buffer          |

| TXCS | console transmit control status      |

| TXDB | console transmit data buffer         |

| TRIS | translation buffer invalidate single |

TBCHK translation buffer check

• MicroVAX I implements these IPRs uniquely:

ICCS interval clock control/status

register

CADR cache disable

MCESR machine check error summary

IORESET initialize bus

The MicroVAX architecture specifies that physical addresses can be up to 30 bits long. A physical address on MicroVAX I is 23 bits long, allowing a physical address space of eight megabytes. (The MicroVAX I physical address space is covered in more detail in Chapter 2 of this manual.)

The differences between the VAX and MicroVAX architectures have been outlined here. The differences between the MicroVAX architecture, and the MicroVAX I implementation of that architecture have also been discussed. For more information about VAX architecture, see the VAX Architecture Handbook, EB-19580-20.

For more information about the MicroVAX I implementation of the MicroVAX architecture, see Chapter 2 of this manual, "Programming Interface." The MicroVAX instruction set is listed in Appendix E.

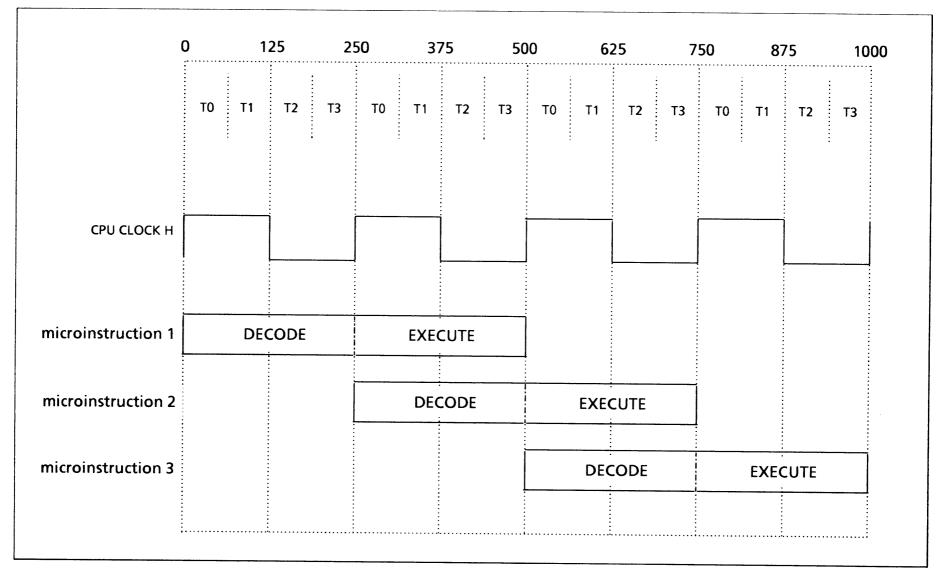

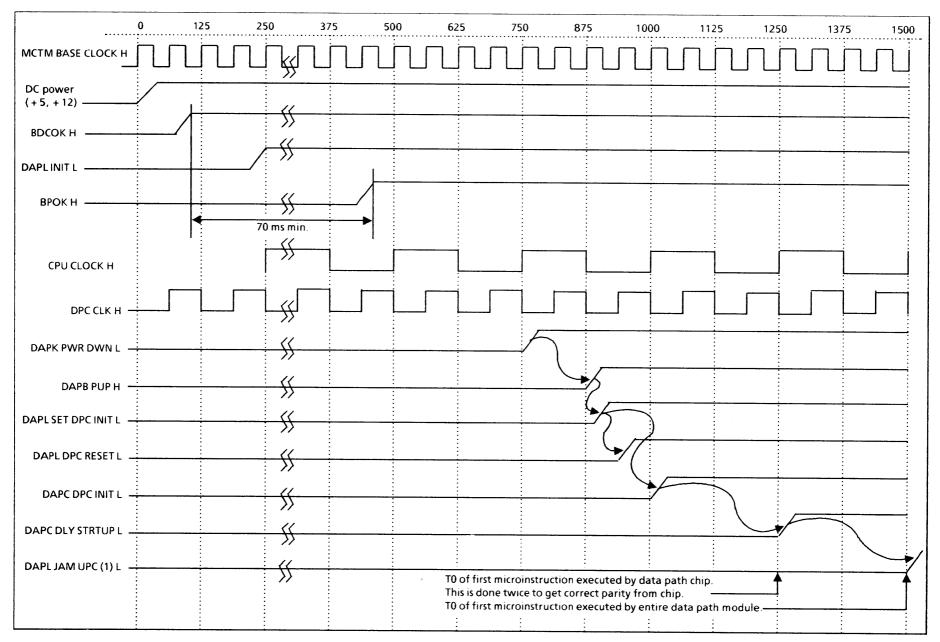

# **System Timing**

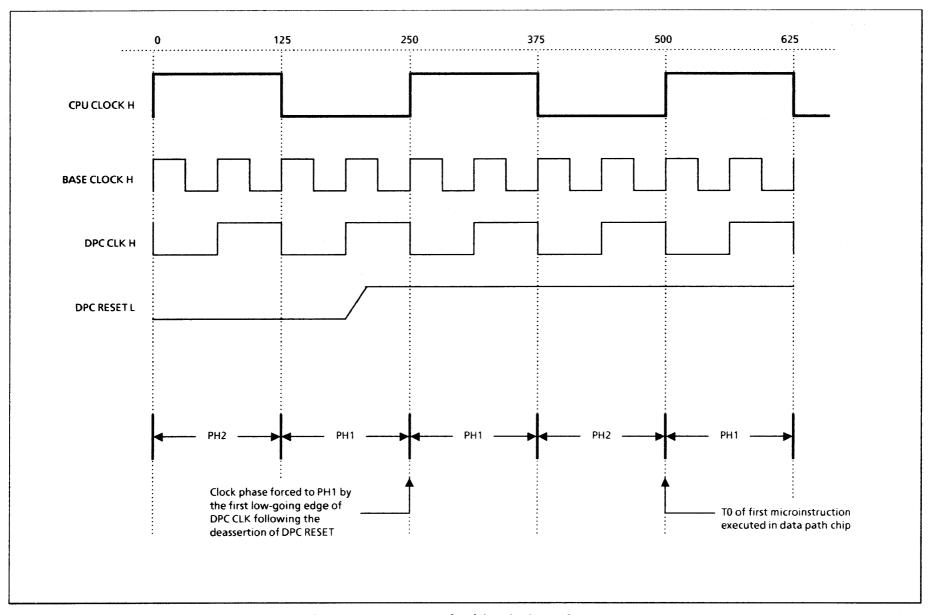

The MicroVAX I system clocks are generated on the CPU memory controller module (MCT). A basic clock with a 64 MHz frequency is generated by a crystal oscillator. All the other clocks in the data path (DAP) and memory controller (MCT) modules are derived from this basic clock.

MicroVAX I is a pipelined, microprogrammed machine. The basic microcycle is 250 ns, and the pipeline is one deep. A new microinstruction on the DAP module is accessed every 250 ns, and requires two 250 ns microcycles to complete. The first 250 ns is DECODE, and the second 250 ns is EXECUTE. The EXECUTE microcycle of the first microinstruction is overlapped with the DECODE microcycle of the next microinstruction. Thus, one microinstruction is retired every 250 ns.

The main clock on the data path module (CPU CLOCK) has a symmetrical 250 nanosecond period. The start of a microcycle is defined as occurring on the leading edge of this clock and is referred to as T0. The trailing edge of the clock occurs 125 ns later.

This timing is illustrated in Figure 1-4.

The memory controller module implements a separate micromachine which cycles at 125 ns to accomplish memory-related activities.

**Figure 1-4. Microinstruction Timing**

# **System Bus Summary**

The system buses which interconnect the modules in the MicroVAX I system are the memory data bus (MDB), the memory control bus (MCB), and the extended LSI-11 bus (Q22 bus). (Those buses that are completely contained within a module are not discussed in this section.)

The memory data bus and the memory control bus connect the two CPU modules (DAP and MCT). The memory data bus is implemented using an over-the-top 50-pin cable. It is a 32-bit bidirectional data bus. The 8-bit memory control bus is implemented using the CD interconnect on the backplane. The remaining lines on the CD interconnect are used for clock distribution, status, and miscellaneous control logic. Slots 1 and 2 on the backplane are reserved for the two CPU modules as both must be placed in Q22/CD slots (see Figure 1-3).

The Q22 bus connects the CPU to the system's memory and peripheral I/O devices. Four basic kinds of transactions take place on the bus:

- Power up/down signal sequencing

- Transfer of bus mastership from the CPU to a direct memory access (DMA) device

- Transfer of data between a bus master and a slave

- Interrupts to the CPU

Most of the bus interface logic is located on the memory controller module. The data path module contains logic to handle power up and down signal sequencing and interrupts. Chapter 9 of this manual, "Q22 Bus Controller," describes the bus transactions in more detail.

For more information about extended LSI-11 bus signals and protocols in general, see the handbook *Microcomputers and Memories*, EB-20912-20.

This chapter is a brief overview of the MicroVAX I system components. For more detail about the MicroVAX I system, see the MicroVAX I Owner's Manual, EK-KD32A-OM, or the MicroVAX I Field Service Print Set, MP-01896-01.

The rest of this manual describes the MicroVAX I processor.

# Chapter 2 Programming Interface

This chapter contains programming information for the KD32-AA and KD32-AB CPUs. It describes the physical address space, the internal processor registers available to the software, how the bootstrap works, what Microverify and the console microcode do, and what happens during exceptions and interrupts.

# **Physical Address Space**

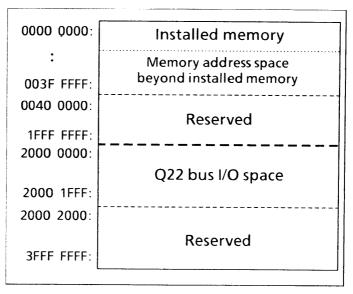

The MicroVAX architecture specifies that physical addresses may be up to 30 bits long. A physical address on MicroVAX I is 23 bits long, providing a physical address space of eight megabytes; four megabytes are in memory space, and four megabytes are in I/O space. Address bit <29> is used to select memory or I/O space, and bits <21:0> select an address within memory or I/O space. Address bit <28> is not part of the 23-bit physical address, but it is used as an internal state flag, called the no-cache flag, to indicate that the address is located in shared memory and should not be cached. Address bits <27:22> are ignored. Physical memory starts at address 00000000 (hex) and is contiguous to the end of installed memory (up to 4 megabytes, address 00400000 hex).

The I/O space is largely empty, containing only Q22 bus I/O space, which is the first 8K bytes (20000000 to 20001FFF). Bit <29> is set in physical address references to I/O space, and bits <21:13> are ignored.

Figure 2-1. MicroVAX I Physical Memory

#### **Address Translation**

MicroVAX I implements full VAX memory management, so virtual addresses are translated to physical addresses just as they are for the VAX minicomputers.

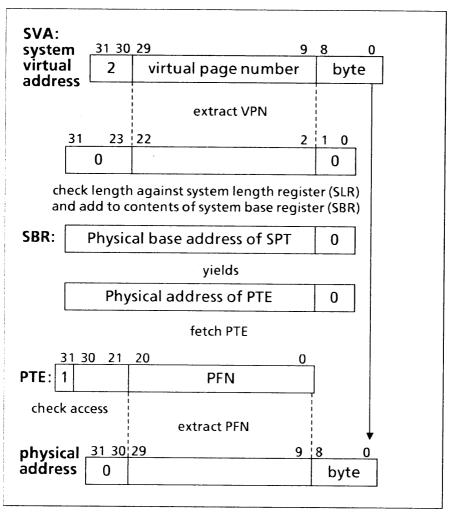

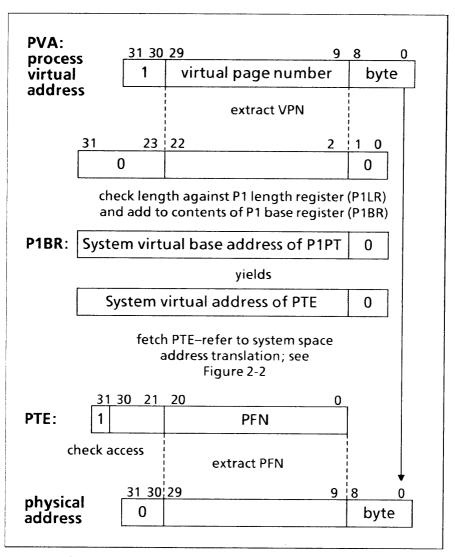

MicroVAX I virtual addresses are 32-bits long, allowing a virtual address space of 4 gigabytes. Virtual address space is divided into process space (low-addressed half) and system space (high-addressed half). Process space is again divided into the P0 region and the P1 region.

When memory management is enabled, system and process space virtual addresses are translated into physical addresses by means of page table entries (PTEs). Virtual memory is partitioned into 512-byte pages; there is one PTE for each page of virtual memory. Each PTE has this format:

| 31           | 30  | 27            | 26            | 25   | 21 | 20  | 0                |

|--------------|-----|---------------|---------------|------|----|-----|------------------|

| valid<br>bit | 1 - | ection<br>eld | modify<br>bit | rese |    | fra | ge<br>me<br>nber |

A physical address is formed for a given virtual address as follows. Bits <31:30> of a virtual address select one of three page tables, each of which contains PTEs for that region of memory:

```

<31:30>=2 selects the system page table (SPT)

<31:30>=1 selects the P1 page table (P1PT)

<31:30>=0 selects the P0 page table (P0PT)

```

Bits <29:9> of the virtual address, called the virtual page number (VPN), are used as a longword index into the selected page table to select the corresponding PTE. Each page table has a length associated with it for determining virtual addresses that are out of bounds.

Once the PTE for the page that contains the given virtual address is found, bits <20:0> of the PTE (the page frame number, or PFN) form bits <29:9> of the physical address. Bits <8:0> of the given virtual address form bits <8:0> of the physical address. Thus, bit <29> of the physical address comes from bit <20> of the PTE, and bit <28> of the physical address comes from bit <19> of the PTE.

Figure 2-2 shows the translation from a system virtual address to a physical address, Figure 2-3 shows the translation from a P0 virtual address to a physical address, and Figure 2-4 shows the translation from a P1 virtual address to a physical address.

Figure 2-2. System Virtual to Physical Translation

Figure 2-3. PO Virtual to Physical Translation

Figure 2-4. P1 Virtual to Physical Translation

## I/O Space Programming Constraints

If either bit <29> or bit <28> of a MicroVAX I physical address is set, certain programming constraints apply. Again, note that bit <28> is not used as part of the physical address, but as the no-cache flag. If this flag is set, the physical address is subject to the same constraints that apply to an I/O space address. The following considerations apply when bit <29> or bit <28> is set in a physical address:

- The data at the specified physical address are not cached.

- Only byte and word-aligned accesses are allowed. Thus, the physical address must be on a byte boundary for instructions using a length attribute of byte, and on an even-byte boundary for instructions using a length attribute of word. Instructions using a length attribute other than byte or word are not allowed.

- In certain devices, byte accesses to word-length registers produce unpredictable results.

- String, quad, floating point, and field references result in undefined behavior.

# **Internal Processor Registers**

There are 64 internal processor registers (IPRs) in the MicroVAX I processor register space. These registers can only be accessed by a Move to Processor Register (MTPR) instruction, or a Move from Processor Register (MFPR) instruction. MTPR and MFPR instructions must be executed in kernel processor mode.

The MicroVAX I internal processor registers can be grouped into four categories, as follows.

- 1. Registers that are implemented as defined by the VAX architecture.

- 2. Registers that are implemented uniquely by the MicroVAX I system.

- 3. Registers to which access is allowed, but which have no effect on the MicroVAX I system; these registers are read as zero, and no operation is performed for writes.

- 4. Registers to which access is not allowed; an access results in a reserved operand fault.

Table 2-1 lists each internal processor register and its category.

The following paragraphs describe all of the registers that are uniquely implemented in MicroVAX I (category 2). The System Identification (SID) register and the four console terminal registers are also described. Although these are in category 1 (implemented as defined by the VAX architecture), some of the bits are uniquely defined for MicroVAX I where allowed by the architecture.

**Table 2-1. Internal Processor Registers**

| Reg          |                            |          |      | Cate- |

|--------------|----------------------------|----------|------|-------|

| No.          | Register Name              | Mnemonic | Type | gory  |

| 0            | Kernel Stack Pointer       | KSP      | R/W  | 1     |

| 1            | Executive Stack Pointer    | ESP      | R/W  | 1     |

| 2            | Supervisor Stack Pointer   | SSP      | R/W  | 1     |

| 3            | User Stack Pointer         | USP      | R/W  | 1     |

| 4            | Interrupt Stack Pointer    | ISP      | R/W  | 1     |

| 5            | Reserved                   |          |      | 4     |

| 6            | Reserved                   |          |      | 4     |

| 7            | Reserved                   |          |      | 4     |

| 8            | P0 Base Register           | P0BR     | R/W  | 1     |

| 9            | P0 Length Register         | P0LR     | R/W  | 1     |

| A            | P1 Base Register           | P1BR     | R/W  | 1     |

| $\mathbf{B}$ | P1 Length Register         | P1LR     | R/W  | 1     |

| $\mathbf{C}$ | System Base Register       | SBR      | R/W  | 1     |

| D            | System Length Register     | SLR      | R/W  | 1     |

| $\mathbf{E}$ | Reserved                   |          |      | 4     |

| F            | Reserved                   |          |      | 4     |

| 10           | Process Control Block Base | e PCBB   | R/W  | 1     |

| 11           | System Control Block Base  | e SCBB   | R/W  | 1     |

| 12           | Interrupt Priority Level   | IPL      | R/W  | 1     |

| 13           | AST Level                  | ASTLVL   | R/W  | 1     |

| 14           | Software Interrupt Reques  | stSIRR   | W    | 1     |

- 1 = implemented as defined by VAX architecture

- 2 = implemented by MicroVAX I uniquely

- 3 = read as zero, no operation on writes

- 4 = access not allowed; results in reserved operand fault

Table 2-1. Continued

| Reg | •                                  |          |      | Cate- |

|-----|------------------------------------|----------|------|-------|

| No. | Register Name                      | Mnemonic | Type | gory  |

| 15  | Software Interrupt<br>Summary      | SISR     | R/W  | 1     |

| 16  | Reserved                           |          |      | 4     |

| 17  | CMI Error Register                 | CMIERR   |      | 4     |

| 18  | Interval Clock Control             | ICCS     | R/W  | 2     |

| 19  | Next Interval Count                | NICR     | W    | 3     |

| 1A  | Interval Count                     | ICR      | R    | 3     |

| 1B  | Time of Year                       | TODR     | R/W  | 3     |

| 1C  | Console Storage Receiver<br>Status | CSRS     | R/W  | 4     |

| 1D  | Console Storage Receiver<br>Data   | CSRD     | R    | 4     |

| 1E  | Console Storage Transmit Status    | CSTS     | R/W  | 4     |

| 1F  | Console Storage Transmit Data      | CSTD     | W    | 4     |

| 20  | Console Receive C/S                | RXCS     | R/W  | 1     |

| 21  | Console Receive D/B                | RXDB     | R    | 1     |

| 22  | Console Transmit C/S               | TXCS     | R/W  | 1     |

| 23  | Console Transmit D/B               | TXDB     | W    | 1     |

| 24  | Translation Buffer Disable         | e TBDR   | R/W  | 3     |

- 1 = implemented as defined by VAX architecture

- 2 = implemented by MicroVAX I uniquely

- 3 = read as zero, no operation on writes

- 4 = access not allowed; results in reserved operand fault

Table 2-1. Continued

| Reg        |                                   |          |      | Cate- |

|------------|-----------------------------------|----------|------|-------|

| No.        | Register Name                     | Mnemonic | Type | gory  |

| 25         | Cache Disable                     | CADR     | R/W  | 2     |

| 26         | Machine Check Error<br>Summary    | MCESR    | R/W  | 2     |

| 27         | Cache Error                       | CAER     | R/W  | 3     |

| 28         | Accelerator Control/Status        | s ACCS   |      | 4     |

| 29         | Accelerator Maintenance           | ACCR     |      | 4     |

| 2A         | Reserved                          |          |      | 4     |

| 2B         | Reserved                          |          |      | 4     |

| 2C         | Writable Control Store<br>Address | WCSA     |      | 4     |

| 2D         | Writable Control Store<br>Data    | WCSB     |      | 4     |

| 2E         | Reserved                          |          |      | 4     |

| <b>2</b> F | Reserved                          |          |      | 4     |

| 30         | SBI Fault/Status                  | SBIFS    | R/W  | 3     |

| 31         | SBI Silo                          | SBIS     | R    | 3     |

| 32         | SBI Silo Comparator               | SBISC    | R/W  | 3     |

| 33         | SBI Maintenance                   | SBIMT    | R/W  | 3     |

| 34         | SBI Error Register                | SBIER    | R/W  | 3     |

| 35         | SBI Timeout Address               | SBITA    | R    | 3     |

| 36         | SBI Quadword Clear                | SBIQC    | W    | 3     |

- 1 = implemented as defined by VAX architecture

- 2 = implemented by MicroVAX I uniquely

- 3 = read as zero, no operation on writes

- 4 = access not allowed; results in reserved operand fault

Table 2-1. Continued

| Reg | •                                    |          |      | Cate- |

|-----|--------------------------------------|----------|------|-------|

| No. | Register Name                        | Mnemonic | Type | gory  |

| 37  | Initialize Bus                       | IORESET  | W    | 2     |

| 38  | Memory Management<br>Enable          | MAPEN    | R/W  | 1     |

| 39  | Translation Buffer<br>Invalidate All | TBIA     | W    | 1     |

| 3A  | Translation Buffer Invalidate Single | TBIS     | W    | 1     |

| 3B  | Translation Buffer Data              | TBDATA   | R/W  | 3     |

| 3C  | Microprogram Breakpoint              | MBRK     | R/W  | 3     |

| 3D  | Performance Monitor<br>Enable        | PMR      | R/W  | 3     |

| 3E  | System Identification                | SID      | R    | 1     |

| 3F  | Translation Buffer Check             | TBCHK    | W    | 1     |

- 1 = implemented as defined by VAX architecture

- 2 = implemented by MicroVAX I uniquely

- 3 = read as zero, no operation on writes

- 4 = access not allowed; results in reserved operand fault

#### **Interval Clock Control/Status Register**

The MicroVAX I processor includes a 10 millisecond interval timer. The Interval Clock Control/Status Register (ICCS) contains the interrupt enable bit for the timer. The interrupt enable bit is bit <6>. It is cleared when the system is booted.

| 31 | 7 | 6                | 5 | 0 |

|----|---|------------------|---|---|

| 0  |   | interrupt enable | 0 |   |

When the interrupt enable bit is set, an interrupt request is generated at interrupt priority level 16 (hex) when the 10 ms timer overflows. When the interrupt enable bit is clear, the timer overflow is ignored; no interrupt is generated.

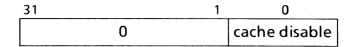

#### **Cache Disable Register**

The memory controller module of the processor contains an 8 KB cache. The Cache Disable Register (CADR) contains the disable bit for the cache. The disable bit is bit <0>. It is cleared during machine initialization so that the cache is enabled.

When the cache disable bit is set, the cache is disabled. When the cache disable bit is clear, the cache is enabled.

#### **Machine Check Error Summary Register**

The Machine Check Error Summary Register (MCESR) is always read as zero. A write to this register clears the machine-check-in-progress flag. This flag is an internal state flag that is set when a machine check occurs.

This flag should be cleared by software when a machine check has been handled. If a second machine check occurs while this flag is set, the CPU halts with a halt code of 5, indicating that a double machine check has occurred. (See Table 2-6 in this chapter for a description of the console halt codes.)

#### **Initialize Bus Register**

The Initialize Bus Register (IORESET) is write-only; an attempt to read this register causes a reserved operand fault.

Any write to this register causes a system reset which initializes the processor and causes a Q22 bus initialization sequence.

#### **System Identification Register**

The System Identification Register (SID) is a read-only constant register that specifies the processor type. The information in the SID register is used for error logs and to check engineering change order (ECO) levels.

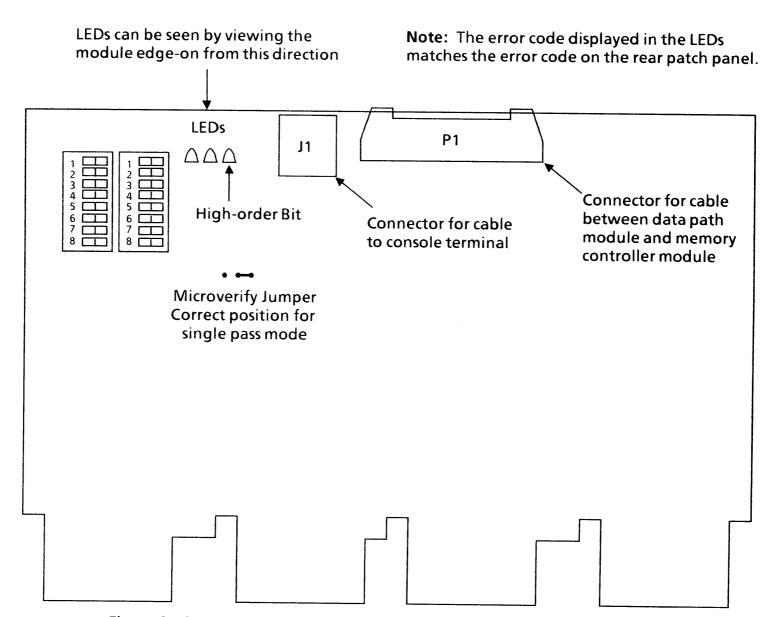

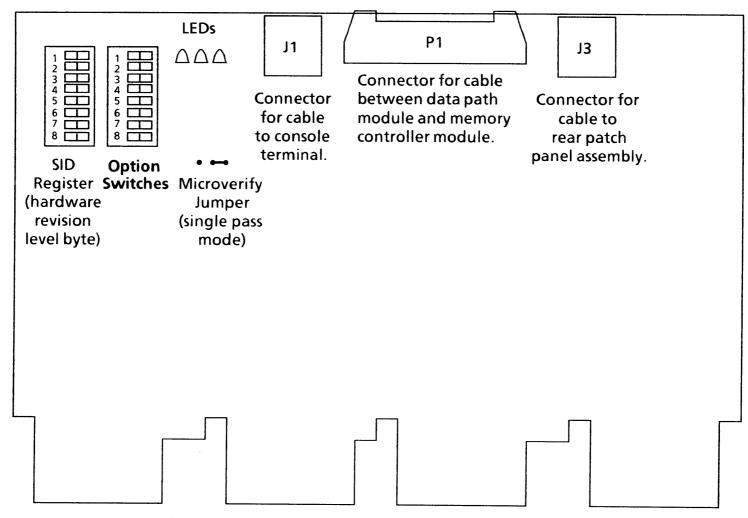

The SID register is four bytes wide. The three highorder bytes are built by the processor microcode and the low-order byte is set by an eight-switch DIP on the data path module. The high-order byte contains a number that uniquely identifies the processor; the MicroVAX I processor is identified by the number 7.

If the processor is the KD32-AA CPU with F<sub>-</sub> and G<sub>-</sub>floating point, bit 16 of the SID register is a 0. If the processor is the KD32-AB CPU with F<sub>-</sub> and D<sub>-</sub>floating point, bit 16 of the SID register is a 1.

| 31 |   | 24 | 23   | 17    | 16 | 15             | 8    | 7   | 0                       |

|----|---|----|------|-------|----|----------------|------|-----|-------------------------|

|    | 7 |    | rese | erved |    | micro<br>revis | sion | rev | dware<br>vision<br>evel |

## **Console Terminal Registers**

The console terminal is accessed through four internal registers. Two registers are associated with receiving from the terminal, and two with writing to the terminal. In each direction there is a control/status register and a data buffer register. The bit assignments for each register are described in the following paragraphs.

# **Console Receive Control/Status Register (RXCS)**

Bits <31:8> and <5:0> of the RXCS register are read as zero and ignored on writes.

Bit 7 is the done bit. It is a read-only bit that is set by the console whenever a character is received. The done bit is initialized to 0 at bootstrap time and is cleared when the RXDB (console receive data buffer) register is read.

Bit 6 is the interrupt enable bit. When this bit is set, an interrupt is generated at interrupt priority level 14 (hex) when the done bit is set. An interrupt is also generated if the done bit is already set when the software sets the interrupt enable bit. The interrupt enable bit is set to 0 at bootstrap time, and can be read or written by software.

| 31 | 8 | 7    | 6         | 5 |   | 0 |

|----|---|------|-----------|---|---|---|

| 0  |   | done | interrupt |   | 0 |   |

|    |   |      | enable    |   |   |   |

#### **Console Receive Data Buffer Register (RXDB)**

This register is a read-only register.

Bits <31:16> and <14:8> of the RXDB register are read as zero.

Bit 15 is the error bit. If the received character contains an error, this bit is set.

Bits < 7:0> are the data field. This field contains the actual character received by the console.

| 31 |   | 16 | 15    | 14 | 8 | 7 |      | 0 |

|----|---|----|-------|----|---|---|------|---|

|    | 0 |    | error |    | 0 |   | data |   |

#### **Console Transmit Control/Status Register (TXCS)**

Bits <31:8> and <5:0> of the TXCS register are read as zero and ignored on writes.

Bit 7 is the ready bit. It is a read-only bit that is set at bootstrap time, and whenever the console transmitter is not busy. The ready bit is cleared when the TXDB (console transmit data buffer) register is written.

Bit 6 is the interrupt enable bit. If this bit is set by software, an interrupt is generated at interrupt priority level 14 (hex) when the ready bit becomes set. If the ready bit is already set and software sets the interrupt enable bit, an interrupt is also generated.

| 31 | 8 | 7     | 6                   | 5 |   | 0 |

|----|---|-------|---------------------|---|---|---|

| 0  |   | ready | interrupt<br>enable |   | 0 |   |

#### **Console Transmit Data Buffer Register (TXDB)**

This register is a write-only register.

Bits <31:12 > of the TXDB register are ignored.

Bits <11:8> form the ID field. The encoding in this field determines whether characters are written to the console terminal, or whether internal functions are executed. If <11:8>=0, the character contained in bits <7:0> of the TXDB register is written to the console terminal. If <11:8>=F, the internal function

specified by bits <7:0> of the TXDB register is performed. If <11:8>=1-E, a reserved operand fault occurs.

Bits <7:0> are the data field. This field contains the actual character transmitted to the console if the ID field is 0. If the ID field contains the value F, the data field specifies the internal function to be performed. The internal functions are encoded as shown in Table 2-2.

| 31 |         | 12 | 11   | 8    | 7 | 0                  |

|----|---------|----|------|------|---|--------------------|

|    | ignored |    | ID f | ield |   | acter or<br>action |

**Table 2-2. TXDB Register Encoding**

| TXDB |                                                                      |  |  |  |

|------|----------------------------------------------------------------------|--|--|--|

|      | <11:0> Internal Function                                             |  |  |  |

| F00  | no operation                                                         |  |  |  |

| F01  | no operation                                                         |  |  |  |

| F02  | boot the system                                                      |  |  |  |

| F03  | clear the restart-in-progress flag                                   |  |  |  |

| F04  | clear the boot-in-progress flag                                      |  |  |  |

| F05  | causes the system to enter console mode (halt code 2; see Table 2-6) |  |  |  |

| F06  | illegal; causes a machine check                                      |  |  |  |

| F07  | illegal; causes a machine check                                      |  |  |  |

| F08  | write 000 to the diagnostic LEDs (all LEDs on)                       |  |  |  |

| F09  | write 001 to the LEDs (on, on, off)                                  |  |  |  |

| F0A  | write 010 to the LEDs (on, off, on)                                  |  |  |  |

| F0B  | write 011 to the LEDs (on, off, off)                                 |  |  |  |

| F0C  | write 100 to the LEDs (off, on, on)                                  |  |  |  |

| F0D  | write 101 to the LEDs (off, on, off)                                 |  |  |  |

| F0E  | write 110 to the LEDs (off, off, on)                                 |  |  |  |

| F0F  | write 111 to the LEDs (all LEDs off)                                 |  |  |  |

# MicroVAX I System Bootstrap

The data path module of the processor contains an EPROM (erasable programmable read-only memory). The EPROM contains the primary bootstrap. The purpose of the primary bootstrap is to load a secondary bootstrap. In some cases, the secondary bootstrap is the entire system image. In other cases, the secondary bootstrap loads the system image. The primary bootstrap, then, is a set of instructions that cause

additional instructions to be loaded until the complete computer program is stored in memory.

The primary bootstrap checks each device that could contain the secondary bootstrap or a system image. It checks these devices in a predetermined order. When the primary bootstrap finds the first device (usually a disk drive) that contains a secondary bootstrap or an appropriate system image, the primary bootstrap causes the secondary bootstrap or system image supplied by the device to be copied into memory and executed.

In short, the primary bootstrap provided with the MicroVAX I system does the following:

- Initializes the machine to a known state

- Locates, determines the size of, and tests the memory

- Locates and reads the secondary bootstrap or system image into memory

- Begins execution of the secondary bootstrap or system image

**Note:** The last 16-bit word of the primary bootstrap must be the twos complement of the sum of all previous 16-bit words. See the section titled "Microverify" in this chapter for more information about this checksum.

#### **Bootstrapping Methods**

There are five ways to bootstrap a MicroVAX I system.

The data path module contains an eight-switch DIP called the option switches. Option switches 3 and 4 determine the series of activities that the processor attempts during power on. If either "boot, halt" or "warm start, boot, halt" is the action set in the switches, the system boots when system power is turned on.

- If "boot, halt" is the action set in the switches, the system boots when a Halt instruction is executed in kernel mode. If "warm start, boot, halt" is the action set in the switches and warm start fails, the system boots when a Halt instruction is executed in kernel mode.

- The system boots when the boot command is entered from console mode. (Pressing the Halt button on the front panel places the system in console mode. The Halt button must be pressed again to unlatch it before the boot command is entered.) The boot command is described below.

- When the Restart button on the front panel is pressed, the system examines option switches 3 and 4 for the recovery action. If "boot, halt" is the action set in the switches, the system boots when the Restart button is pressed. If "warm start, boot, halt" is the action set in the switches and warm start fails when the Restart button is pressed, the system boots. (The Halt button must be latched out for the Restart button to work.)

**Note:** With all software currently sold by DIGITAL for the MicroVAX I, pressing the Restart button always causes the system to reboot.

• The system boots when the value F02 (hexadecimal) is written to the console transmit data buffer register (TXDB).

When the MicroVAX I system is booted by one of these methods, the console microcode searches for 64K bytes of good memory. If 64K bytes of good memory cannot be found, the boot fails and a message is displayed on the console terminal.

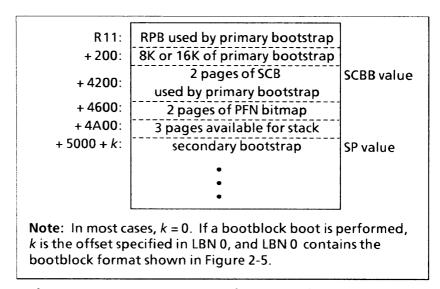

If sufficient memory is found, the primary bootstrap stored in the EPROM is read into successive locations in memory, starting at the base address of the found memory plus 0200 (hexadecimal) and continuing for 8K or 16K bytes (depending on whether an 8K or 16K EPROM is installed). When the transfer is complete, a jump to the beginning of the primary bootstrap is executed (that is, a jump to the base address plus 0200). The primary bootstrap is then executed using the information in the following general registers:

| R0  | zero, or the four character device name specified in the boot command |

|-----|-----------------------------------------------------------------------|

| R1  | settings of the option switches                                       |

| R5  | zero, or the flag value specified in the boot command                 |

| R10 | program counter at the time boot was requested                        |

| R11 | processor status at the time boot was requested                       |

| AP  | halt code (see Table 2-6)                                             |

| SP  | base address of the found memory plus 0200 (hexadecimal)              |

When the primary bootstrap is executed, it locates the appropriate secondary bootstrap or system image and reads it into memory.

#### **Boot Command**

The format of the console boot comand is:

The two acceptable forms of the command, therefore, are:

where /n is an optional hexadecimal flag value that is passed to the primary and secondary bootstrap in general register R5, and xxxx is an optional device name that is passed to the primary bootstrap in general register R0. If no flag value or device name is specified, the value zero is passed to R5 and R0.

The device name must be exactly four characters. Table 2-3 lists the allowable device names.

DUA0 disk or diskette unit 0

DUA1 disk or diskette unit 1

DUA2 disk or diskette unit 2

DUA3 disk or diskette unit 3

PRA0 MRV11 PROM

XQA0 DEQNA

Table 2-3. Device Names

Table 2-4 lists the hexadecimal flags for the boot command parameter /n that are meaningful to the primary bootstrap. Leading zeros need not be supplied.

**Note:** Other flags not listed in Table 2-4 may be meaningful to various operating systems available for the MicroVAX I. For example, the boot command B/1 invokes a conversational boot when the operating system software is MicroVMS.

**Table 2-4. Boot Command Flags**

| Bit | Hex Flag |                                                                                                                                                                                                                                                                                                          |

|-----|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No. | Value    | Flag Name and Meaning                                                                                                                                                                                                                                                                                    |

| 3   | 00000008 | BOOTBLOCK – Secondary boot from bootblock. When this bit is set, the primary bootstrap skips the normal operation, which is to search the volume as a Files-11 volume. Instead, the primary bootstrap reads logical block number 0 of the volume and tests it for conformance with the bootblock format. |

| 4   | 00000010 | DIAGNOSTIC – Diagnostic boot.<br>When this bit is set, the secondary<br>bootstrap is the image called<br>[SYS0.SYSMAINT]DIAGBOOT.EXE.                                                                                                                                                                    |

| 6   | 00000040 | HEADER – Image header. If this bit is not set, the primary bootstrap transfers control to the first byte of the secondary bootstrap file. If this bit is set, the primary bootstrap transfers control to the address of the secondary bootstrap obtained from that file's image header.                  |

| 7   | 08000080 | NOTEST – Memory test inhibit.<br>This flag disables parity checking<br>during boot.                                                                                                                                                                                                                      |

| 8   | 00000100 | SOLICT – Solicit file name. When this bit is set, the primary bootstrap prompts for the name of a secondary bootstrap file.                                                                                                                                                                              |

Table 2-4. Continued

| Bit<br>No. | Hex Flag<br>Value | Flag Name and Meaning                                                                                                                                                                                                        |

|------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9          | 00000200          | HALT – Halt before transfer. When this bit is set, it causes a Halt instruction to be executed before transferring control to the secondary bootstrap.                                                                       |

| 31:28      | X0000000          | TOPSYS. X can be any value from 0 through F (hex). The TOPSYS flag changes the top level directory name for system disks with multiple operating systems. For instance, if $X = 1$ , the top level directory name is [SYS1]. |

#### **Bootstrap Operation**

The primary bootstrap stored in the EPROM contains code that:

- initializes the system control block (SCB),

- initializes the restart parameter block (RPB),

- initializes a PFN (page frame number) bit map and the relevant RPB fields,

- selects a boot device, and

- performs a Files-11 ODS2, bootblock, PROM, or down-line load boot.

The primary bootstrap finds the device which contains the secondary bootstrap in one of two ways.

1. If a device name is specified in the boot console command, that device is searched for the secondary bootstrap.

2. If no device name is specified, and option switch number 1 is off (which is the default position), the following devices are searched in the order listed here until the secondary bootstrap is found, or the list is exhausted.

All diskette drives in ascending unit order

All fixed disk drives in ascending unit order

MRV11 PROM

DEQNA for down-line loading

If option switch number 1 is on, the primary bootstrap bypasses the diskettes and disks and searches only the MRV11 PROM and the DEQNA for the secondary bootstrap.

# **Booting from Disk**

For the system to boot successfully from diskette or disk, the RQDX1 controller must be configured at Q22 bus address 772150 (octal). The module is shipped this way from the factory. (For more information about configuring the RQDX1 module, see the "System Configuration" section of the *MicroVAX I Owner's Manual*, EK-KD32A-OM.)

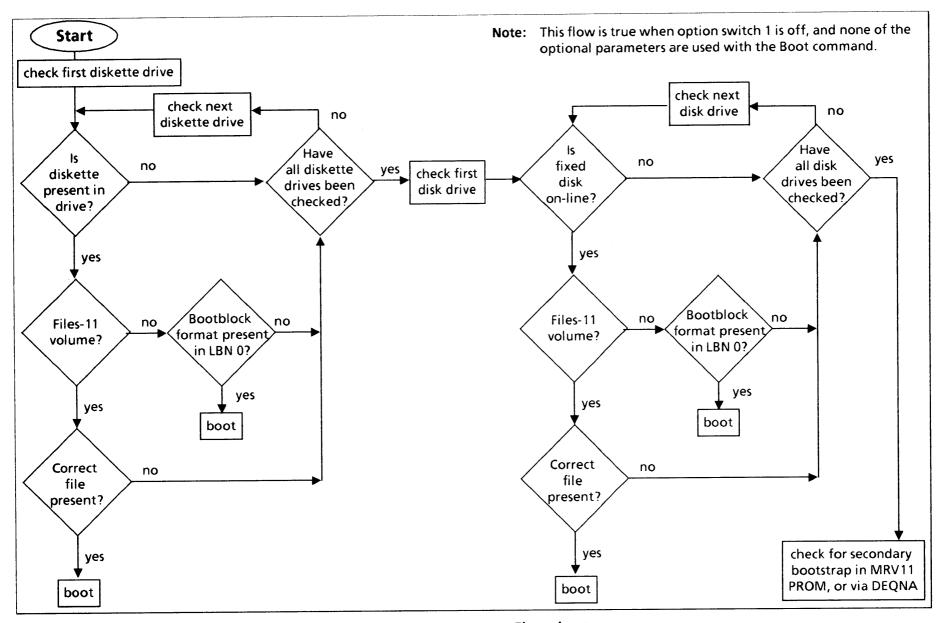

The primary bootstrap begins by searching the diskette drives for the secondary bootstrap. (This is assuming that if the boot console command is used to bootstrap the system, none of the optional parameters are specified.) The primary bootstrap checks the first diskette drive to determine if a diskette is installed. If no diskette is present, the next diskette drive is checked.

If a diskette is present, the primary bootstrap determines if it is a Files-11 volume. If it is, the primary bootstrap searches for the file

#### [SYS0.SYSEXE]SYSBOOT.EXE

which contains the secondary bootstrap. If this file is found, the system boots. If this file is not found, the primary bootstrap checks the next diskette drive.

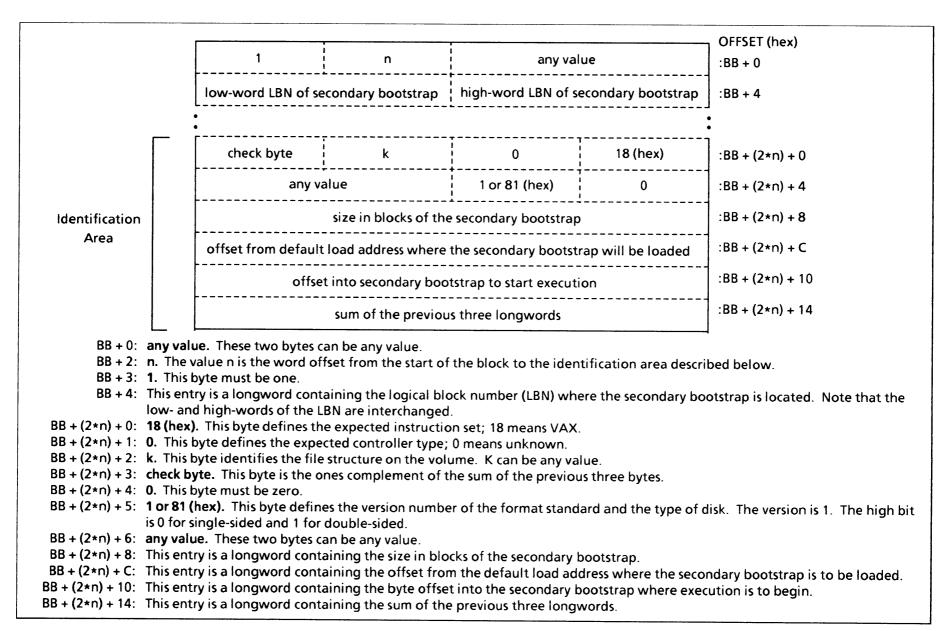

If a diskette is present on the diskette drive being checked but it is not a Files-11 volume, the primary bootstrap checks for the bootblock format in logical block number (LBN) 0 of the diskette. Figure 2-5 shows the bootblock format.

If LBN 0 of the diskette contains the bootblock format, the system boots. If the bootblock format is not present, the primary bootstrap checks the next diskette drive.

If the primary bootstrap cannot find the secondary bootstrap on any diskette, it checks the fixed disk drives in the same manner. First, it checks whether the fixed disk drives are on-line. Then, for every drive on-line, it checks if the disk is a Files-11 volume. If it is, and the file [SYS0.SYSEXE]SYSBOOT.EXE is present, the system boots.

If the disk is not a Files-11 volume, the primary bootstrap checks for the bootblock format in LBN 0. If the bootblock format is present, the system boots.

The sequence just described occurs unless the boot console command is used with any of these hexadecimal flags specified in the /n parameter:

bit <3> = BOOTBLOCK bit <4> = DIAGNOSTIC bits <31:28> = TOPSYS