# PERKIN-ELMER

# OS/32 SYSTEM LEVEL

**Programmer Reference Manual**

The information in this document is subject to change without notice and should not be construed as a commitment by The Perkin-Elmer Corporation. The Perkin-Elmer Corporation assumes no responsibility for any errors that may appear in this document.

The software described in this document is furnished under a license, and it can be used or copied only in a manner permitted by that license. Any copy of the described software must include the Perkin-Elmer copyright notice. Title to and ownership of the described software and any copies thereof shall remain in The Perkin-Elmer Corporation.

The Perkin-Elmer Corporation assumes no responsibility for the use or reliability of its software on equipment that is not supplied by Perkin-Elmer.

The Perkin-Elmer Corporation, Data Systems Group, 2 Crescent Place, Oceanport, New Jersey 07757

© 1981, 1983, 1984 by The Perkin-Elmer Corporation

Printed in the United States of America

# TABLE OF CONTENTS

| PRE  | FACE                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                    | <b>v</b> i                                                                                                                |  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|--|

| CHAI | PTERS                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                           |  |

| 1    | OS/32 SU                                                                                                                                                              | BSYSTEMS                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                           |  |

|      | 1.1                                                                                                                                                                   | INTRODUCTION OS/32 Multiprocessing Support                                                                                                                                                                                                                                                                                                                                                         | 1-1<br>1-2                                                                                                                |  |

|      | 1.2<br>1.2.1<br>1.2.1.1<br>1.2.2<br>1.2.3<br>1.2.4<br>1.2.5<br>1.2.6<br>1.2.7<br>1.2.8<br>1.2.9<br>1.2.10<br>1.2.11<br>1.2.12<br>1.2.13<br>1.2.14<br>1.2.15<br>1.2.16 | Job Accounting Subsystem  Memory Management Subsystem  Timer Management Subsystem  File Management Subsystem  Input/Output (I/O) Subsystem  Error Recording Subsystem  Memory Diagnostics Subsystem  Loader and Segmentation Subsystem  Basic Data Communications Subsystem  Console Monitor Subsystem  Command Processor Subsystem  System Initialization Subsystem  Internal Interrupt Subsystem | 1-3<br>1-5<br>1-8<br>1-10<br>1-11<br>1-12<br>1-13<br>1-13<br>1-14<br>1-14<br>1-14<br>1-15<br>1-16<br>1-17<br>1-17<br>1-17 |  |

| 2    | PRIVILEG                                                                                                                                                              | ED TASKS                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                           |  |

|      | 2.1                                                                                                                                                                   | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                       | 2-1                                                                                                                       |  |

|      | 2.2<br>2.2.1<br>2.2.2                                                                                                                                                 | EXECUTIVE TASKS (E-TASKS) Writing Executive Tasks (E-Tasks) OS/32 Data Structures Used by Executive Tasks (E-Tasks)                                                                                                                                                                                                                                                                                | 2-2<br>2-2<br>2-3                                                                                                         |  |

|      | 2.3                                                                                                                                                                   | PRIVILEGED USER TASKS (U-TASKS)                                                                                                                                                                                                                                                                                                                                                                    | 2-7                                                                                                                       |  |

|      | 2 /                                                                                                                                                                   | ENTACNOCHIC MACKC (D. MACKC)                                                                                                                                                                                                                                                                                                                                                                       | 2 7                                                                                                                       |  |

48-040 F00 R03 i

# CHAPTERS (Continued)

PROGRAMMING IN A MODEL 3200MPS SYSTEM MULTIPROCESSING ENVIRONMENT

| 1        |     | 3.1            | INTRODUCTION                                                                                               | 3-1          |

|----------|-----|----------------|------------------------------------------------------------------------------------------------------------|--------------|

|          |     | 3.2            | DESIGNING TASKS TO RUN ON A MULTIPROCESSING SYSTEM                                                         | 3-1          |

| !<br>!   |     | 3.3            | PREPARING AN AUXILIARY PROCESSING UNIT (APU) FOR TASK EXECUTION                                            | 3-2          |

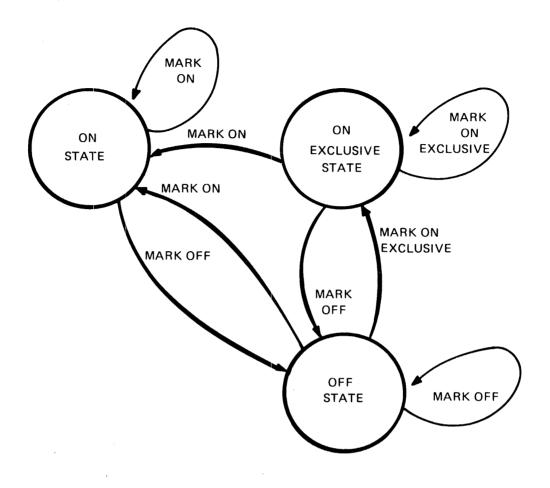

| 1        |     | 3.3.1<br>3.3.2 | Queue Assignments<br>Auxiliary Processing Unit (APU) Operating<br>States                                   | 3-2<br>3-3   |

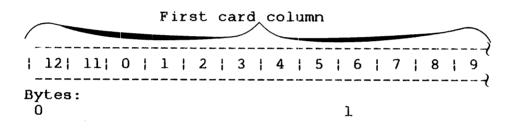

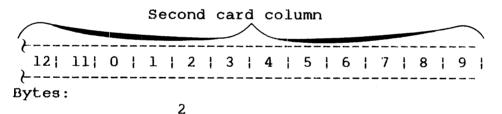

| !        |     |                | APU-Only Queue Operating States Logical Processing Unit (LPU) Mapping                                      | 3-4<br>3-6   |

| <b>!</b> |     | 3.4            | ASSIGNING TASKS TO A PROCESSOR QUEUE                                                                       | 3-7          |

| <b>!</b> | _   | 3.5<br>3.5.1   | CONTROLLING TASK ORDER OF EXECUTION Changing Auxiliary Processing Unit (APU)                               | 3-8          |

|          |     | 3.5.2          | Task Queue Ordering Monitoring and Preempting Auxiliary Processing                                         | 3-8          |

| 1        |     | 3.5.3          | Unit (APU) Task Execution Transferring a Task from an Auxiliary Processing Unit (APU) to the Central       | 3-10         |

| !        |     | 3.5.4          | Processing Unit (CPU) Internal Task Control of Auxiliary Processing                                        | 3-17         |

| :<br>    |     | 3.5.5          | Unit (APU) Execution Verifying Task Transfer to an Auxiliary                                               | 3-18         |

|          |     | 3.5.6          | Processing Unit (APU) Customizing Auxiliary Processing Unit (APU) Fault and Supervisor Call (SVC) Handling | 3-19<br>3-19 |

| <b>¦</b> |     |                | PREVENTING MEMORY ACCESS CONFLICTS Avoiding System Deadlock                                                | 3-21<br>3-21 |

| 1 1      |     | 3.7            | MEASURING REAL-TIME PERFORMANCE ON A MODEL 3200MPS SYSTEM                                                  | 3-22         |

|          | ÷ , | 3.8            | WHERE TO GO FOR MORE INFORMATION                                                                           | 3-25         |

|          | 4   | SUPERVISO      | OR CALL (SVC) INTERCEPTION                                                                                 |              |

|          |     | 4.1            | INTRODUCTION                                                                                               | 4-1          |

|          |     | 4.2            | HOW SUPERVISOR CALL (SVC) INTERCEPTION WORKS                                                               | 4-2          |

|          |     | 4.3            | PREPARING A TASK FOR SUPERVISOR CALL (SVC) INTERCEPTION                                                    | 4-4          |

|          |     | 4.3.1<br>4.3.2 | Request Descriptor Block (RDB) Buffers<br>Circular List for Request Descriptor Block                       | 4-4          |

|          |     | 4.3.3          | (RDB) Buffers Task Event Trap                                                                              | 4-6<br>4-7   |

ii

# CHAPTERS (Continued)

5

| 4.4                                                                          | CREATING INTERCEPT PATHS (ICREATE)                                          | 4-7                                                                                          |

|------------------------------------------------------------------------------|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| 4.5                                                                          | HOW TO CREATE A PSEUDO DEVICE OR TASK WITH ICREATE                          | 4-8                                                                                          |

| 4.6                                                                          | USE OF GENERIC NAMING FOR PSEUDO DEVICES AND TASKS                          | 4-9                                                                                          |

| 4.7                                                                          | FUNCTIONAL SUMMARY OF SUPERVISOR CALL (SVC) INTERCEPTION                    | 4-10                                                                                         |

| 4.8                                                                          | FULL AND MONITOR CONTROL INTERCEPT PATHS                                    | 4-11                                                                                         |

| 4.9                                                                          | HOW INTERCEPT PATHS HANDLE SUPERVISOR CALLS (SVCs) OCCURRING AT END OF TASK | 4-12                                                                                         |

| 4.10                                                                         | TERMINATING THE INTERCEPTED SUPERVISOR CALLS (SVCs)                         | 4-13                                                                                         |

| 4.11                                                                         | HOW TO REMOVE INTERCEPT PATHS                                               | 4-13                                                                                         |

| 4.12                                                                         | ERROR HANDLING                                                              | 4-13                                                                                         |

| 4.13.2<br>4.13.3<br>4.13.4<br>4.13.5<br>4.13.6<br>4.13.7<br>4.13.8<br>4.13.9 | IPROCEED Macro IROLL Macro ITERM Macro ITRAP Macro IERRTST Macro            | 4-15<br>4-16<br>4-21<br>4-23<br>4-24<br>4-26<br>4-27<br>4-28<br>4-29<br>4-30<br>4-32<br>4-34 |

| OS/32-SU                                                                     | PPORTED INPUT/OUTPUT (I/O) DEVICES                                          |                                                                                              |

| 5.1                                                                          | INTRODUCTION                                                                | 5-1                                                                                          |

| 5.2<br>5.2.1<br>5.2.2                                                        | VERTICAL FORMS CONTROL (VFC)<br>Horizontal Tabs<br>Theory of Operation      | 5-1<br>5-2<br>5-2                                                                            |

| 5.3                                                                          | CARD READERS                                                                | 5-3                                                                                          |

| 5.4                                                                          | CARD READER/PUNCH DEVICES                                                   | 5-4                                                                                          |

ł

48-040 F00 R03 iii

# CHAPTERS (Continued)

|   | 5.5          | TELETYPE (TTY) READER/PUNCH                                            | 5-6                |

|---|--------------|------------------------------------------------------------------------|--------------------|

|   | 5.6          | TELETYPE (TTY) KEYBOARD/PRINTER                                        | 5-7                |

|   | 5.7          | PAPER TAPE EQUIPMENT                                                   | 5-7                |

|   | 5.8          | LINE PRINTERS                                                          | 5-8                |

|   | 5.9          | TAPE CASSETTE                                                          | 5-8                |

|   | 5.10.1       | MAGNETIC TAPE  Standard Input/Output (I/O)  Gapless Input/Output (I/O) | 5-9<br>5-9<br>5-10 |

|   | 5.11         | DISK STORAGE                                                           | 5-10               |

|   | 5.12         | FLOPPY DISK                                                            | 5-11               |

|   | 5.13         | VIDEO DISPLAY UNIT (VDU) TERMINALS                                     | 5-12               |

|   | 5.14         | 8-LINE INTERRUPT MODULE                                                | 5-12               |

|   | 5.15         | DIGITAL MULTIPLEXOR (MUX)                                              | 5-12               |

|   | 5.16         | CONVERSION EQUIPMENT                                                   | 5-13               |

|   | 5.17         | ANALOG INPUT CONTROLLER (AIC)                                          | 5-13               |

|   | 5.18         | ANALOG OUTPUT CONTROLLER (AOC)                                         | 5-14               |

|   | 5.19         | DIGITAL INPUT/OUTPUT (DIO) CONTROLLER                                  | 5-15               |

| ; | 5.20         | ETHERNET DATA LINK CONTROLLER (EDLC)                                   | 5-16               |

|   | APPEND I XES | 3                                                                      |                    |

| ţ | A (          | OS/32-SUPPORTED INPUT/OUTPUT (I/O) DEVICES                             | <b>A-1</b>         |

|   |              | SUPPORTED VERTICAL FORMS CONTROL (VFC) CHARACTER SET                   | B-1                |

|   | FIGURES      |                                                                        |                    |

|   | 1-1          | Typical Model 3200MPS System Configuration                             | 1-3                |

| 1 |              | Valid APU Operating States<br>Valid APU Oueue Operating States         | 3-3<br>3-5         |

iv 48-040 F00 R03

# FIGURES (Continued)

| 4-1<br>4-2        | Request Descriptor Block<br>System Task Buffer List (Standard Circular List)                                                               | 4-4<br>4-6          |      |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|

| 5-1<br>5-2        | Random Field Format<br>Analog Output Data Format                                                                                           | 5-14<br>5-14        |      |

| TABLES            |                                                                                                                                            |                     |      |

| 1-1               | PERKIN-ELMER OS/32 SOFTWARE SUPPORT                                                                                                        | 1-4                 | ł    |

| 2-1<br>2-2        | OS/32 DATA STRUCTURES MACRO LIBRARY MTM DATA STRUCTURES MACRO LIBRARY                                                                      | 2-4<br>2-7          | <br> |

| 3-1<br>3-2<br>3-3 | QUEUE PRIORITY ASSIGNMENTS<br>TIMER MACROS<br>ADDITIONAL INFORMATION SOURCES FOR MODEL 3200MPS<br>SYSTEM PROGRAMMING                       | 3-9<br>3-23<br>3-25 | <br> |

| 4-1<br>4-2<br>4-3 | SYSTEM MACROS FOR SVC INTERCEPTION<br>ERROR CODES RETURNED FOR INTERCEPT MACROS<br>VALID COMBINATIONS FOR SVC, MODE AND NAME<br>PARAMETERS | 4-1<br>4-14<br>4-18 |      |

| INDEX             |                                                                                                                                            | IND-1               | !    |

48-040 F00 R03 v

|  | ų |  |

|--|---|--|

|  |   |  |

|  |   |  |

#### **PREFACE**

This manual describes operating system features intended for use by system programmers, system analysts, designers, engineers and training instructors.

Chapter 1 presents an overview of the operating system and software subsystems it supports. Chapter 2 describes privileged task types supported by OS/32. Chapter 3 describes the techniques used in writing system level control programs that increased throughput offered advantage of the Perkin-Elmer Model 3200MPS System. Chapter 4 contains functional description of the supervisor call (SVC) interception The vertical forms control (VFC) feature is feature. Chapter 5, along with other device-independent device-dependent features supported by OS/32.

Revision 03 is intended for use with the OS/32 R07.2 software release or higher. It introduces a change in the method of task execution by the auxiliary processing units (APUs) within the Therefore, Model 3200MPS System. Chapter 3 has been totally reorganized. Material related to OS/32 SVCs is no longer included in this manual. This material is now documented in the OS/32 Supervisor Call (SVC) Reference Manual.

For information on the contents of all Perkin-Elmer 32-bit manuals, see the 32-Bit Systems User Documentation Summary.

## CHAPTER 1 OS/32 SUBSYSTEMS

#### 1.1 INTRODUCTION

Perkin-Elmer OS/32 is a general-purpose, event-driven operating system for Perkin-Elmer 32-bit computer systems. Custom versions of OS/32 are created through the use of a system generation program (Sysgen/32) that provides parameters for tailoring OS/32 to a specific installation. The combined hardware and software capabilities of a Perkin-Elmer 32-bit computer system provide support for all phases of program and system development. OS/32 supports concurrent multiprogramming, with up to 252 user programs written in any of the supported languages. The program development facilities are designed to minimize the time and effort needed to test, debug and integrate application programs and systems. In addition, the OS/32 command language allows complex jobs to be performed with minimum operator intervention.

OS/32 incorporates a powerful interrupt handling capability at the task level. This capability permits a task to be interrupted during its normal execution sequence by a variety of hardware and software conditions.

The OS/32 virtual task manager (VTM) allows the memory requirements of a task running under OS/32 to exceed available task memory.

The roll function allows segments of a task to be rolled out to disk until enough memory is available for the entire task. In real-time applications, rolling is commonly used to queue low priority tasks while tasks of higher priority are active. The roll eligibility of a task is established when the task is linkedited. However, a task option is provided to prevent rolling of a task when necessary (e.g., when the task must be able to respond to real-time events).

VTM has a virtual memory capability that allows tasks consisting of up to 16Mb of code and data to execute in as little as 128kb of memory. This feature is provided by the OS/32 linkage editor. See the OS/32 Link Reference Manual for more information.

A basic data communications facilities package is supplied with OS/32. This package also provides support for higher level Perkin-Elmer data communications products.

The scope and power of the operating system can be extended through the following Perkin-Elmer OS/32 companion products.

- Multi-terminal monitor (MTM)

- Reliance

MTM is a subsystem monitor that uses the subtasking capabilities of OS/32 to provide a time-sliced, interactive program development environment for up to 64 concurrent terminal users. MTM simultaneously supports both on-line terminal users and batch background tasks. MTM terminal users are also provided with an input/output (I/O) spooler for use with slow speed devices.

Reliance is a transaction software system, consisting of the integrated transaction controller (ITC), data management system (DMS/32), and industry standard COBOL. ITC allocates system resources, develops screen formats, and controls terminals. DMS/32 supervises disk allocation and data access.

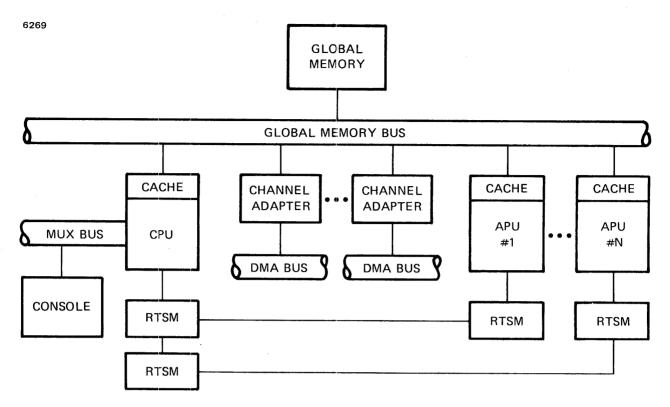

# 1.1.1 OS/32 Multiprocessing Support

OS/32 provides a transparent multiprocessing capability for use with the Perkin-Elmer Model 3200MPS System. This system consists of one central processing unit (CPU) and from one to nine auxiliary processing units (APUs) (see Figure 1-1). A task can execute on an APU without any special preparation, unless it is going to take advantage of certain features specific to the multiprocessing system (e.g., APU assignment, APU control, etc.). See the OS/32 Supervisor Call (SVC) Reference Manual for more information.

OS/32 defines a set of logical processing units (LPUs) that are used to schedule tasks to APU queues for execution on an APU. Tasks are assigned to an LPU that is mapped to an APU queue. The logical processor mapping table (LPMT) defined by OS/32 contains the mapping arrangement between the LPUs and APU execution queues. (More than one LPU can be mapped to an APU queue.)

Each APU in a Model 3200MPS System is assigned a unique identifying number and is assigned to an APU queue. (More than one APU can be assigned to a queue.) Tasks on the APU queue execute on an APU assigned to the queue.

If a task is mainly computation intensive, executing that task on an APU increases overall system performance. An I/O-intensive task, if directed to an APU, decreases system performance since each I/O request requires the task to be transferred back to the CPU for OS/32 I/O support services.

The main performance advantage of a multiprocessing system is achieved when a problem is broken down into parts so that several tasks on several processors can work on the problem at the same time. See Chapter 3 for more information on programming within a Perkin-Elmer Model 3200MPS System environment.

1-2 48-040 F00 R03

Figure 1-1 Typical Model 3200MPS System Configuration

#### 1.2 SOFTWARE SUBSYSTEMS

OS/32 consists of the following subsystems:

- Task management

- Job accounting

- Memory management

- Timer management

- File management

- I/O management

- Error recording and reporting

- Memory diagnostics

- Loader and segmentation

- Basic communications

- Console monitor

- Command processor

- System initialization

- Internal interrupt

- Optional user supervisor call 14 (SVC14)

- Floating point

Table 1-1 summarizes the software supported by OS/32.

TABLE 1-1 PERKIN-ELMER OS/32 SOFTWARE SUPPORT

| TYPE ;          | SOFTWARE PRODUCT                                                                                                                                                                                                                       | STANDARD                 | OPTIONAL                 |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--------------------------|

| Program         | Task management                                                                                                                                                                                                                        | ) x                      |                          |

| develop-        | Job accounting                                                                                                                                                                                                                         | ×                        |                          |

| ment            | Memory management                                                                                                                                                                                                                      | X                        |                          |

| į               | Timer management                                                                                                                                                                                                                       | X                        |                          |

| i               | File management                                                                                                                                                                                                                        | X<br>  X                 | j<br>1                   |

| i               | I/O management Error recording and reporting                                                                                                                                                                                           | i X<br>I X               |                          |

| i               | Memory diagnostics                                                                                                                                                                                                                     | l x                      |                          |

| •               | Loader and segmentation                                                                                                                                                                                                                | x                        |                          |

| !               | Console monitor                                                                                                                                                                                                                        | x                        |                          |

|                 | Command processor                                                                                                                                                                                                                      | x                        |                          |

|                 | Floating point                                                                                                                                                                                                                         | x                        |                          |

|                 | Internal interrupt subsystem                                                                                                                                                                                                           | x                        |                          |

| Ì               | ITC*                                                                                                                                                                                                                                   |                          |                          |

| i               | Writable control store (WCS)                                                                                                                                                                                                           | 1                        | x                        |

| Ï               | MTM                                                                                                                                                                                                                                    | 1                        | ¦ x                      |

|                 |                                                                                                                                                                                                                                        |                          |                          |

|                 | Automatic interactive debugging                                                                                                                                                                                                        |                          | 1                        |

| debugging       | system (AIDS)                                                                                                                                                                                                                          | l x                      |                          |

| ;               | DEBUG/32                                                                                                                                                                                                                               | i                        | ¦ x                      |

| Data baga i     | DMS*                                                                                                                                                                                                                                   |                          |                          |

| Data base       | CMD ~                                                                                                                                                                                                                                  | 1                        | l x                      |

| manage-<br>ment |                                                                                                                                                                                                                                        | 1                        |                          |

|                 |                                                                                                                                                                                                                                        |                          | ,<br>                    |

| Data            | Asynchronous data communications                                                                                                                                                                                                       | x                        | į                        |

| communi-        | Character synchronous communica-                                                                                                                                                                                                       | 1                        | <b>!</b>                 |

| cations         | tions                                                                                                                                                                                                                                  | ¦ x                      | 1 -                      |

|                 | Bit synchronous communications                                                                                                                                                                                                         |                          | x                        |

| 1               | 2780/3780 RJE emulation                                                                                                                                                                                                                | }                        | l x                      |

| !               | 3270 emulation                                                                                                                                                                                                                         |                          | x                        |

|                 | HASP/32                                                                                                                                                                                                                                |                          | x                        |

|                 | Ethernet communications                                                                                                                                                                                                                | ; x                      | l                        |

|                 |                                                                                                                                                                                                                                        |                          |                          |

| Tanguage        | Common microcode aggembler                                                                                                                                                                                                             | !                        | !                        |

| Languages       | Common microcode assembler                                                                                                                                                                                                             |                          | <br>  x                  |

| Languages       | (MICROCAL)                                                                                                                                                                                                                             | <br> <br>                | <br>  x                  |

| Languages       | (MICROCAL)<br>Common assembly language/32                                                                                                                                                                                              | <br> <br> <br>  x        | <br>  x<br>              |

| Languages       | (MICROCAL)<br>  Common assembly language/32<br>  (CAL/32)                                                                                                                                                                              | <br> <br> <br>  x<br>  x | <br>  x<br> <br>         |

| Languages       | (MICROCAL)   Common assembly language/32   (CAL/32)   CAL macro/32                                                                                                                                                                     |                          | <br>  x<br> <br> <br>    |

| Languages       | (MICROCAL)   Common assembly language/32   (CAL/32)   CAL macro/32<br>  FORTRAN VII development (D)                                                                                                                                    |                          | <br>                     |

| Languages       | (MICROCAL)   Common assembly language/32   (CAL/32)   CAL macro/32   FORTRAN VII development (D)   compiler                                                                                                                            |                          | 1<br>1<br>1<br>1         |

| Languages       | (MICROCAL)   Common assembly language/32   (CAL/32)   CAL macro/32   FORTRAN VII development (D)   compiler   FORTRAN VII global optimizing (O)   compiler                                                                             |                          | 1<br>1<br>1<br>1         |

| Languages       | (MICROCAL)   Common assembly language/32   (CAL/32)   CAL macro/32   FORTRAN VII development (D)   compiler   FORTRAN VII global optimizing (O)                                                                                        |                          | <br> <br> <br> <br>  x   |

| Languages       | (MICROCAL)   Common assembly language/32   (CAL/32)   CAL macro/32   FORTRAN VII development (D)   compiler   FORTRAN VII global optimizing (O)   compiler   FORTRAN VII universal optimizing   (Z) compiler                           |                          | <br> <br> <br> <br>  x   |

| Languages       | (MICROCAL)   Common assembly language/32   (CAL/32)   CAL macro/32   FORTRAN VII development (D)   compiler   FORTRAN VII global optimizing (O)   compiler   FORTRAN VII universal optimizing   (Z) compiler   COBOL*                  |                          | <br> <br> <br>  x<br>  x |

| Languages       | (MICROCAL)   Common assembly language/32   (CAL/32)   CAL macro/32   FORTRAN VII development (D)   compiler   FORTRAN VII global optimizing (O)   compiler   FORTRAN VII universal optimizing   (Z) compiler   COBOL*   BASIC Level II |                          | x                        |

| Languages       | (MICROCAL)   Common assembly language/32   (CAL/32)   CAL macro/32   FORTRAN VII development (D)   compiler   FORTRAN VII global optimizing (O)   compiler   FORTRAN VII universal optimizing   (Z) compiler   COBOL*                  |                          | x                        |

1

TABLE 1-1 PERKIN-ELMER OS/32 SOFTWARE SUPPORT (Continued)

| TYPE             | SOFTWARE PRODUCT                                                                                                                                                                       | STANDARD | OPTIONAL |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|

| Utilities        | Link<br>  Edit<br>  Text<br>  Source Updater<br>  Copy<br>  Library Loader<br>  Macro Library<br>  Sort/Merge II<br>  Patch<br>  OS/32 Spooler<br>  SPL/32<br>  Fastchek<br>  Fastback | X        | x x      |

| <br> -<br> -<br> | Account Reporting Backup Error Reporting Disk Dump Dump Print Mirror Disk Synchronizaton                                                                                               |          | x        |

<sup>\*</sup> ITC, COBOL and DMS/32 comprise the Perkin-Elmer Reliance software system designed for transaction processing.

#### 1.2.1 Task Management Subsystem

The task management subsystem allocates processor time for each of the tasks executing in an OS/32 multitasking environment. The task manager determines the order in which each task gains processor control on a user-defined priority basis. Task priority levels range from 0 to 254 (0 being the highest priority level). Of these 255 priority levels, 10 through 249 are available for user-written tasks, while 1 through 9 and 250 through 254 are reserved for system use.

The task manager maintains four priority levels for each task:

- Maximum

- Task

- Run

- Dispatch

Maximum priority, set by Link, is the highest priority level (i.e., the smallest number) that can be assigned to a task. Task priority is the priority that is currently assigned to a task. Initially, task priority is set when the task is linked, but this priority can be changed after the task is loaded. However, task priority can never be set higher than the maximum priority set by Link.

Run priority can be set dynamically to a value ranging from the task priority to task priority plus n. The value of n is based on the behavior of the task. Run priority can only be set for tasks that have dynamic time-slice/priority scheduling enabled. If dynamic scheduling is not enabled, a task's run priority is equal to its task priority. Currently, only MTM enables dynamic time-slice/priority scheduling.

A dispatched task usually has a priority level equal to its task priority, even if dynamic scheduling is enabled. Nevertheless, if a higher priority task requires specific system resources (e.g., a disk directory or bit map) that are currently controlled by a lower priority task, the dispatch priority of this lower priority task is raised to the priority of the higher priority task waiting for the resource. When a task releases control of a system resource, its dispatch priority is reset to its run priority.

Tasks competing for processor time are maintained in priority order on a task control block (TCB) queue known as the ready queue. Tasks competing for both memory and processor time are maintained in priority order on the roll-in queue. Tasks at the same priority level are serviced on a round-robin basis; i.e., tasks are added to the ready queue or roll-in queue behind tasks of the same priority.

In the absence of time-slicing, once a task gains control of the processor, it continues executing until it voluntarily relinquishes that control or is preempted by a higher priority task. A task will relinquish control of the processor to another task when one of the following occurs.

- It is paused by the system operator.

- It is cancelled by the system operator, user or another task.

- A higher priority task becomes ready due to an external event, such as the completion of an outstanding I/O request.

- It executes an SVC that places it in a wait, paused or dormant state.

- It initiates I/O to a device.

- Its time-slice expires.

1-6 48-040 F00 R03

After the task relinquishes control of the processor, it is returned to the ready queue, where its TCB is placed behind the TCBs of tasks of equal priority. This allows the other tasks on the queue to be given a turn on the processor.

To determine which task should have control of the processor, the task manager chooses the highest priority task among those on the ready queue, the roll-in queue, and any currently executing task. If a task is chosen from one of the queues, the currently executing task is placed back on the ready queue and the chosen task becomes the current task.

The task manager supports two types of time-slicing:

- System time-slice

- Dynamic time-slice

System time-slicing limits the execution of a task so that round-robin scheduling of priority tasks can take effect. Time-slicing allows tasks of equal priority to receive equal shares of processing time.

At system generation (sysgen), system time-slicing can be enabled through the use of the SLICE command. This allows time-slice scheduling to be activated automatically by the system. Thereafter, the operator SET SLICE command can be used to override the SLICE command.

Dynamic time-slicing is enabled only for MTM subtasks. The dynamic time-slice is calculated as:

slice = 1 + 2\*\*m

Where:

m = task priority - run priority + 1

The slice is measured in units of line frequency clock (LFC) ticks (one LFC tick = 8.333ms).

Run priority is adjusted whenever a task uses up a time-slice, is removed from a wait state, or has its priority modified by the operator SET PRIORITY command. When a task uses up a time-slice, its run priority is adjusted as follows:

1

New run priority = run priority + 1 or task priority + k (whichever is smaller)

#### Where:

Because a task that is placed in a wait state does not use up its last assigned time-slice, the run priority of the task, when it is removed from suspension, is adjusted as follows:

Run priority = run priority - 1 or task priority (whichever is larger)

The task manager also performs intratask context switches to allow tasks to receive and handle task traps in response to synchronous and asynchronous trap-causing events. Synchronous events include task-initiated faults (e.g., arithmetic, memory access, illegal instruction, etc.) and SVC14 traps. Asynchronous events originate outside of a task and include the task queue traps (e.g., I/O and timer completion, SVC6 send message/data and queue parameter, etc.) and the task event traps currently associated only with SVC intercept support.

In addition to task scheduling and task trap support, the task manager handles the state of a task during execution. Task execution state is determined by the setting of the program status word (PSW). The task manager switches or exits tasks from one execution state to another.

#### 1.2.1.1 Task Scheduling on a Model 3200MPS System

The OS/32 task manager uses four different types of queues to facilitate task scheduling on a Model 3200MPS System:

- CPU ready queue

- CPU receive queue

- CPU roll-in queue

- APU execution queue

An APU execution queue can be one of four different types:

- APU idle queue, not serviced by any processor

- APU private queue, serviced by a single APU

- APU shared queue, serviced by several APUs

CPU/APU shared queue, serviced by the CPU whenever its own ready queue is empty and/or by one or more APUs; this is always APU execution queue 0.

Each APU execution queue can be designated either no-priority or priority-ordered. Priority-ordered queues can be either enforced or not enforced, depending upon whether a task put on the top of the queue preempts a currently executing task of lower priority. The CPU ready queue is priority-enforced, and the CPU receive queue is no-priority.

When a task requests processor time on a Model 3200MPS System, the task manager adds the TCB for that task to the CPU ready queue. The task manager selects a task for execution from the queue on a strict priority basis. After selecting a task, the task manager then decides whether the task is to be executed on the CPU or placed on one of the APU queues in the system. A task is transferred to an APU queue for processing only when all of the following conditions are true:

- The task must be executing in the user state, not in the system state.

- The task's "LPU-directed" status must be set. (In MTM, when the load-leveling executive (LLE) is active, subtasks of MTM cannot be LPU-directed unless the user has SVC6 privileges.)

- The task status word (TSW) does not specify CPU-override status. (If the CPU-override status bit of the TSW is set, the task is executed on the CPU.)

When all of the above conditions are true for the highest priority task on the CPU ready queue, the task manager transfers the TCB for that task from the CPU ready queue to an APU queue. If the APU is waiting for the task (i.e., APU processing has been suspended until the task arrives), the TCB becomes the current TCB and execution begins immediately. If the APU is not waiting for the task, the TCB is placed on the APU queue.

Whenever it is not processing a task, the APU continually checks its APU queue. If the APU finds entries on the queue, it will execute the task at the top of the queue.

Once the APU starts a task, the task will execute until it:

- relinquishes control voluntarily (reschedules itself),

- encounters a fault,

- issues an SVC, or

- is returned to the CPU via an operating system request on behalf of a monitoring task, operator command, etc.

The task may reschedule itself to the rear of the APU queue or to the CPU. In a no-priority APU queue, the task is placed at the bottom of the queue. In a priority APU queue, the task is placed behind all tasks of equal or higher priority, or at the queue top if there is no task of equal or higher priority on the queue. In a priority-enforced APU queue, the task is placed on the queue in the same manner as for a priority queue. In addition, whenever the task happens to be placed at the queue top, the operating system executes the preempt procedure to ensure execution of the highest priority tasks, even if a lower priority task is currently executing.

The task is returned to the CPU receive queue if it is rescheduled to the CPU, if a fault occurs, or if an SVC or operating system request occurs. The task waits on the receive queue until the CPU places the task on the CPU ready queue.

If the task is placed on the receive queue as a result of a fault, the task is moved to the CPU ready queue. If the appropriate bits in the TSW are set, the task's TSW location is set to the address of the task trap handler. The task can then be dispatched back to the APU queue.

If the task is placed on the receive queue as a result of issuing an SVC, the task is moved to the CPU ready queue and executed on the CPU until SVC processing is complete. The task can then automatically move back to the APU queue.

Rollable tasks are moved from the roll-in queue to the CPU ready queue and are processed in the same manner as any other task running on a Model 3200MPS System. Rollable tasks may be dispatched to an APU.

Tasks running under MTM will run on APUs as determined by the LLE at a priority scheduled by the priority scheduling mechanism (PSM). When the LLE is active, MTM controls whether the task will be assigned to one of the APUs or to the CPU.

# 1.2.2 Job Accounting Subsystem

The job accounting subsystem reports CPU usage and time elapsed, memory and disk space utilized, and number and length of I/O transfers by device class. The job accounting subsystem contains the:

- Data Collection Facility

- Account Reporting Utility

The Data Collection Facility collects accounting data on all user activities and stores this information in the accounting transaction file (ATF) when the task terminates.

The Account Reporting Utility is designed to accommodate specific customer site requirements. The performance information gathered by the Data Collection Facility is prepared by the Account Reporting Utility for use by system maintenance personnel. Reports can be requested for individual user accounts, summaries of user accounts and system usage. See the OS/32 System Support Utilities Reference Manual.

Through the DISPLAY ACCOUNTING command, the system operator has access to accounting data for one or all tasks in the system. This command also gives MTM users access to accounting data for a task monitored by MTM on their behalf.

NOTE

ţ

i

The OS/32 job accounting subsystem now reports APU usage and time elapsed in a Model 3200MPS System.

#### 1.2.3 Memory Management Subsystem

When a task is loaded, the memory management subsystem dynamically allocates necessary space in memory. OS/32 supports three types of memory:

- Local

- Shared

- System

Local memory is physically contiguous starting from location 0 and contains the operating system, task space and system space.

Shared memory is located above local memory and is not required to be contiguous. Global task common segments located in shared memory can be used by more than one processor.

System memory is shared by all processors in a Model 3200MPS System. System memory contains both local and shared areas. Local memory is used by the CPU and all APUs.

Local memory is allocated on a first-fit basis when sufficient memory is available for a specific task. Free segments are allocated in ascending address order. When no space is available for a task, the memory manager determines which tasks are to be rolled out to ensure that higher priority tasks take precedence. When memory becomes free, adjacent areas are merged together to minimize search time and to provide large free blocks of memory for bigger tasks. System task space is also maintained by the memory manager and is dynamically allocated when a task or device structure is built.

The memory manager maintains task space through free and allocated lists. Segments are allocated dynamically on a first-fit basis by searching the free lists. When free task space is allocated to a segment, it is removed from the free list and connected to the allocated list. This list is called the segment control list (SCL). Similarly, whenever a segment is released, its memory space is removed from the allocated list and connected to (or merged into) the free list.

# 1.2.4 Timer Management Subsystem

The timer management subsystem provides tasks with a set of timer management/maintenance services. These services control all time-dependent functions (e.g., time-slicing, I/O, job accounting and file dating) through the universal clock (UCLOCK).

The following timer queues are maintained by the timer management subsystem:

- Time of day

- Device time-out

- Communications device time-out

- Interval timer

There are several timer routines that service these queues. Entries are placed on the time of day queue and the interval timer queue as a result of SVC2 timer requests. The control blocks on the time of day queue are referred to as timer queue elements (TMQs). The interval timer queue has the same format as the time of day queue but is maintained as a separate queue.

The UCLOCK consists of an LFC and a precision interval clock (PIC). In a 60Hz system, the LFC generates an interrupt every 8.3ms or 120 times per second. In a 50Hz system, the LFC generates an interrupt every 10ms, or 100 times per second. The PIC interrupts when a task's requested time interval has expired or at intervals of 4,096ms, whichever is shorter. If the interval terminates or the time of day is reached, the TMQ is removed from system space and a trap is generated, or the task is removed from timer wait.

In a Model 3200MPS System configuration, the real-time support module (RTSM) provides each processor with a 32-bit real-time counter for timing program execution. These counters are incremented every microsecond by an RTSM lMHz on-board oscillator. The RRTC instruction allows tasks to read the counters. See the Perkin-Elmer Model 3200MPS System Instruction Set Reference Manual for more information.

# 1.2.5 File Management Subsystem

The OS/32 file management subsystem stores and retrieves information for a task on secondary storage devices (disks, floppy disks, etc.). The file manager partitions this storage into smaller areas, called files, that can be used by tasks for data and program storage. In addition, the file manager provides tasks with the following support services for file management:

Allocate creates a file by allocating space on a secondary storage device.

Delete removes a file from a secondary storage device.

Rename changes the name of a file.

Open assigns a logical unit (lu) to a file.

Close cancels the lu assignment.

Fetch examines the attributes of a file.

attributes

Checkpoint ensures that all data in an output buffer is written to a secondary storage device.

Software selects recording density for 6250 bits density per inch (bpi) magnetic tape drives. selection

### 1.2.6 Input/Output (I/O) Subsystem

The I/O subsystem provides a uniform programming interface between the task and external devices. I/O operations can occur in the following task modes:

Wait halts execution until data transfer is completed.

Proceed I/O continues task execution during data transfer.

Halt I/O allows the task to cancel previous proceed I/O requests.

Queued I/O allows a task to queue I/O requests to a busy device and continue execution until the device is free.

A task trap mechanism can be used to report each completed I/O operation. Wait-only and test I/O functions allow the task to synchronize its execution with the completed I/O operations.

48-040 F00 R03 1-13

## 1.2.7 Error Recording Subsystem

The error recording subsystem logs all data on disk errors for the Error Reporting Utility, which analyzes the data and generates reports.

OS/32 memory error recording software supports the memory error log hardware of the Perkin-Elmer Series 3200 processors. Error log hardware keeps a history of the single-bit corrected memory errors. The operating system reads the error log hardware and stores the error information into an internal error log buffer. When the error log buffer is full, its contents are stored on an error recording file with the date and time of the last error recorded. When the error recording file is almost full, a warning message is displayed on the system console indicating that a new error recording file should be allocated or that the Error Reporting Utility should be initiated. The Error Reporting Utility provides reports on the previously recorded error information in the error recording file.

The current error status can be displayed to the system console by using the DISPLAY ERRORS command. The internal error log read-out period can be changed by the system operator.

#### 1.2.8 Memory Diagnostics Subsystem

The memory diagnostics subsystem eliminates inoperable memory areas from the system without affecting task execution. It allows the operating system to execute when portions of real memory have been removed (holes) or when a part of the system is powered down for maintenance. Memory can be tested and marked on and off through the operator MEMORY command or when the operating system is initialized.

The marked-off areas are noted as allocated in the memory map. Memory is marked-on when previously marked-off memory is to be used again. If an irrecoverable memory error occurs during task execution on a Perkin-Elmer Series 3200 processor, the operating system automatically marks off the area occupied by the task.

#### 1.2.9 Loader and Segmentation Subsystem

The OS/32 resident loader is responsible for loading tasks, reentrant libraries, task common (TCOM) segments, and partial images. These tasks and segments must have been built by Link. Each task image generated by Link contains information related to the task (e.g., task options, size, libraries referenced) in a record called the loader information block (LIB). The OS/32 resident loader uses this information to generate data areas, set the task options, create segment tables for the tasks and map the task segments.

1-14 48-040 F00 R03

All user tasks (u-tasks) in OS/32 are built as though they were loaded at physical address 0 in memory. The relocation/protection hardware automatically relocates the task addresses at run-time by using the task segment table. This process is totally transparent to the user.

The loader is also responsible for creating the task environment; allocating roll files; creating, maintaining and deleting segment tables; maintaining a segment control list; and mapping and unmapping partial images.

The task image can be divided into pure and impure segments by specifying the SEGMENTED task option when the task is built by Link. Regardless of the number of times a task is loaded, the loader will allow only one copy of the task's pure segment in memory at any one time. A separate copy of the task's impure segment is loaded each time the task is loaded. The relocation/protection hardware ensures the integrity of pure segments by allowing read-only and execute-only access privileges to those segments.

Access to task common is achieved mnemonically in FORTRAN or assembly programs. The linkages are resolved by Link. Link commands are also used to request read, write and execute privileges for task common blocks. See the OS/32 Link Reference Manual for more information.

## 1.2.10 Basic Data Communications Subsystem

The basic data communications subsystem provides a software interface between tasks and common carrier facilities. Basic data communications facilities allow the user to access remote terminals or computers as though they were locally attached peripherals. For example, with OS/32 Data Communications software, a task performs I/O to a remote terminal in the same manner as I/O to a local device.

In addition to providing device-independent (logical I/O) access to the task, the subsystem provides a device-dependent I/O capability that allows the systems programmer to tailor a communications package to a particular installation. Such a package can include device-dependent and device-independent support of asynchronous line devices as well as device-dependent support of binary synchronous lines.

The OS/32 Basic Data Communications software support package is required for all 32-bit communications products; e.g., HASP, 2780/3780 Remote Job Entry, the zero-bit data link control (ZDLC) Channel Terminal Manager and the Ethernet Data Link Controller (EDLC), which support the synchronous data logic control (SDLC), high-level data link controller (HDLC) and advanced data communications control procedure (ADCCP) protocols.

# 1.2.11 Console Monitor Subsystem

The console monitor subsystem processes all I/O requests directed to the system console device and the system log device from all tasks including the command processor task. The console driver is responsible for intercepting system console I/O requests and for directing them to the console monitor or to another monitor task such as MTM. All I/O operations between the system console and tasks running under MTM are routed to the user's terminal through MTM and not through the console monitor.

When a command is issued from the system console, the console monitor issues an SVC6 to the command processor notifying it of a command to be processed. The command processor interprets the command and issues an SVC6 to the console monitor indicating that it is ready to accept another command.

The console driver is a part of the OS/32 I/O subsystem and is the module that intercepts I/O requests to the system console, processes them, and gives them to MTM or to the console monitor to perform the actual I/O.

The console monitor is the first task dispatched at OS/32 initialization. The console monitor initializes both itself and the dummy device control block (DCB) used by the console driver to intercept requests from the system console. The monitor then issues an SVC6 to start the command processor.

#### 1.2.12 Command Processor Subsystem

The command processor subsystem accepts commands from the system console monitor, decodes them, and calls the appropriate executor. Commands can be input to the command processor by entering them directly through the system console or issuing them through a foreground task that uses the system console as an interactive I/O device. Commands input from a foreground task are executed by the command processor in the same manner as commands entered from the system console. If an error occurs during execution of a command, the command processor outputs an error message to the console.

An extension to the command processor, the command substitution system (CSS) allows commonly performed sequences of operations to be executed with one command. The CSS routines provide the user with the ability to build, execute and control files of operator and MTM commands. The user establishes command files that are called from the user console and executed in the user-defined sequence. In this way, complex operations can be carried out by the user with few commands. These commands are analogous to macro instructions in assembly language.

The CSS provides a set of logical CSS commands to conditionally control the precise sequence of commands to be executed. Parameters can be passed as part of a CSS call so that general sequences can be written that take on specific meaning only when the parameters are substituted. Other calls to CSS files can be imbedded within a CSS file (nested calls).

The command processor normally runs at the second highest priority level after the console monitor in OS/32. This task is strictly trap driven and responds to the SVC6 task queue parameter calls from the console monitor to service a command request. When the command is processed, it signals the console monitor for a new command read via an SVC6 queue parameter call and then enters into a trap wait state. The command processor priority can be decreased by the operator ATTN command. This command can be used in a real-time application environment to allow a task to run at a higher priority than the command processor.

# 1.2.13 System Initialization Subsystem

After the operating system is loaded, the system initialization subsystem initializes the memory diagnostics subsystem, error recording subsystems, and system control blocks and tables in memory. It then dispatches the console monitor, which readies the command processor to accept commands from the system console.

# 1.2.14 Internal Interrupt Subsystem

The internal interrupt subsystem is responsible for:

- handling illegal instruction faults,

- handling arithmetic faults,

- detecting memory faults,

- handling system queue service (SQS) interrupts,

- handling relocation/protection hardware faults,

- handling data format/alignment faults,

- handling power fail and power restore conditions,

- restoring an interrupted task to its previous program state upon resumption of the task,

- handling parameter block errors,

- handling illegal SVCs and SVC interrupts,

- handling machine malfunction interrupts, and

- performing memory image dumps.

Processor-dependent interrupt handlers comprise the internal interrupt subsystem. This subsystem does not support external I/O interrupts; they are handled by the appropriate device drivers.

On a Model 3200MPS System, the CPU handles all fault conditions or interrupts that occur during execution of a task on an APU. Thus, the APU can execute another task while the CPU is handling the fault or interrupt.

# 1.2.15 Optional User Supervisor Call (SVC) Subsystem

SVC14 is provided as an optional SVC that can be defined by the user. On execution, the task receives a task trap for SVC14. See the OS/32 Application Level Programmer Reference Manual for information on how to implement the SVC14 trap feature.

# 1.2.16 Floating Point Subsystem

A task has optional access to single and/or double precision floating point instructions under OS/32. Floating point instructions can be executed through hardware or simulated by software. Systems that do not support floating point options handle all floating point instructions as illegal instructions.

#### CHAPTER 2 PRIVILEGED TASKS

#### 2.1 INTRODUCTION

In a multi-user system, improper use of certain machine instructions, called privileged instructions, can have a detrimental effect on system integrity. Privileged instructions include storage protection setting, interrupt handling, timer control, input/output (I/O) and some processor status-setting instructions. To prevent accidental or intentional misuse of these instructions, OS/32 provides a privileged operating state in which tasks can execute these instructions. In addition to the privileged operating state, OS/32 provides a privileged task state in which tasks can access the file account and bare disk OS/32 supervisor routines.

Only privileged tasks can execute in a privileged operating or task state. OS/32 allows three types of privileged tasks:

- Executive tasks (e-tasks)

- Privileged user tasks (u-tasks)

- Diagnostic tasks (d-tasks)

A task can be linked as a privileged task by specifying one or more of the following task options in the Link OPTION command:

ETASK, ACPRIVILEGE, DISC, DTASK

See the OS/32 Link Reference Manual.

This chapter describes the privileges that are available to each type of privileged task through the Link OPTION command.

48-040 F00 R03 2-1

#### 2.2 EXECUTIVE TASKS (E-TASKS)

E-tasks run with the memory address relocation/protection hardware and are allowed to execute all instructions provided by the hardware. E-tasks always have file account and bare disk privileges. In addition, e-tasks can execute code that modifies or enhances the OS/32 system software. For example, an e-task can modify one of the system modules to enhance an existing OS/32 feature. E-tasks can also function as drivers that support nonstandard peripheral devices. A task can be linked as an e-task by specifying the ETASK task option in the Link OPTION command. The following sections detail the programming considerations that must be taken into account when writing e-tasks.

# 2.2.1 Writing Executive Tasks (E-Tasks)

Because e-tasks execute in a privileged state, certain precautions must be taken when e-tasks are programmed.

When an e-task is executing, no memory address protection or relocation is provided and all interrupts are enabled. The task has access to all machine instructions and memory address space in the system. In addition, the e-task can access system tables and control information via the system pointer table (SPT). The address of the SPT is stored in the halfword at location X'62' in memory.

Link builds the image for an e-task as if it were loaded at absolute location zero. The loader, however, is free to load the e-task into any available memory location. Therefore, an e-task must be coded as if it were positionally independent; an e-task must not contain relocatable code.

Because Link relocates e-task addresses to absolute zero, e-tasks cannot assemble code containing address constants as shown in the following example.

# Example:

SVC7BLK DB X'80',7

DAC ADDR

An e-task must dynamically set the addresses required by the task.

To reference addresses in the +16kb range, use the following technique:

LA UE, BUFSTART

LA UF, BUFEND

LA U3, SVC1PBK

STM UE, SVC1.SAD(U3)

SVC 1,0(U3)

References to addresses exceeding the 16kb range can be made in the following manner.

#### Example:

BASE LA U4,BASE

LA UE,BUFSTART-BASE(U4)

LA UF,BUFEND-BASE(U4)

LA U3,SVC1BLK-BASE(U4)

STM UE,SVC1.SAD(U3)

SVC 1,0(U3)

E-tasks smaller than 16kb must use the no RX3 (NORX3) (CAL/32) instruction to force all RX instructions to the RX1 or RX2 format. The tasks must not contain any RX1 or RX3 instructions with relocatable addresses. See the Common Assembly Language/32 (CAL/32) Programming Reference Manual.

# 2.2.2 OS/32 Data Structures Used by Executive Tasks (E-Tasks)

OS/32 provides two macro libraries that contain OS/32 and multi-terminal monitor (MTM) data structures. The OS/32 data structure macro library is stored in file SYSSTRUC.MLB. Table 2-1 contains a list of the macros and corresponding data structures in this library. Data structures specific to the MTM subsystem are stored in file MTMSTRUC.MLB. The contents of this library are listed in Table 2-2.

Using the OS/32 e-task capability and the data structures available to e-tasks, the system level programmer can incorporate changes or add user-written modules to the source of the OS/32 system modules supplied by Perkin-Elmer.

48-040 F00 R03 2-3

| MACRO        | DATA STRUCTURE                                      |

|--------------|-----------------------------------------------------|

| PARCHO       |                                                     |

| \$ACB        | Directory access control block (ACB)                |

| \$AOPT       | Auxiliary processing unit (APU) options             |

| \$APB        | Auxiliary processor block (APB)                     |

| \$APB\$      | \$APB, \$APRC, \$APS, \$AOPT                        |

|              | Passback reason codes and equates                   |

| \$APS        | APB status codes and equates                        |

| \$APST       | APU status codes, error codes and equates           |

| \$ATF        | Account transaction file (ATF)                      |

| \$CCB        | Channel control block (CCB)                         |

| \$CTX        | U-task context block                                |

| <br>  \$DATB | Device attributes equates                           |

| \$DCB\$      | \$PDCB, \$DDCB ,DCB EQUATE, \$DFLAG, \$DATB, \$DXFL |

| \$DDCB       | Device-dependent device control block (DCB)         |

| \$DDE        | Error log data structure                            |

| \$DFLG       | DCB flags                                           |

| \$DIR        | Primary directory entry                             |

| \$DXFL       | Disk-extended flags                                 |

| <br>  \$EMIL | <br>  System milestone recording entries            |

| \$EFMG       | Bulk device error recording entries                 |

| \$EREGS      | 16 executive registers (El=register 1)              |

| \$ERRC\$     | \$GERC, \$EFMG, \$ESYS, \$EMIL, \$MERC              |

| \$ESYS       | System error recording entries                      |

| \$EVN        | Event node                                          |

| ¦<br>¦\$FCB  | <br>  File control block (FCB).                     |

| \$FCB\$      | FCB and FCB flags                                   |

| \$FDE        | Free block descriptor entry                         |

| \$FFLG       | FCB flags                                           |

| \$FD         | File descriptor (fd)                                |

| \$GERC       | <br>  General error recording information           |

| і<br>¦ \$нв  | <br>  Help subroutine argument block                |

| INTCPARM     | Supervisor call (SVC) intercept information         |

| ¦ \$ICB      | Intercept control block                             |

| ¦ \$IOB      | I/O block                                           |